Image Processing Reference

In-Depth Information

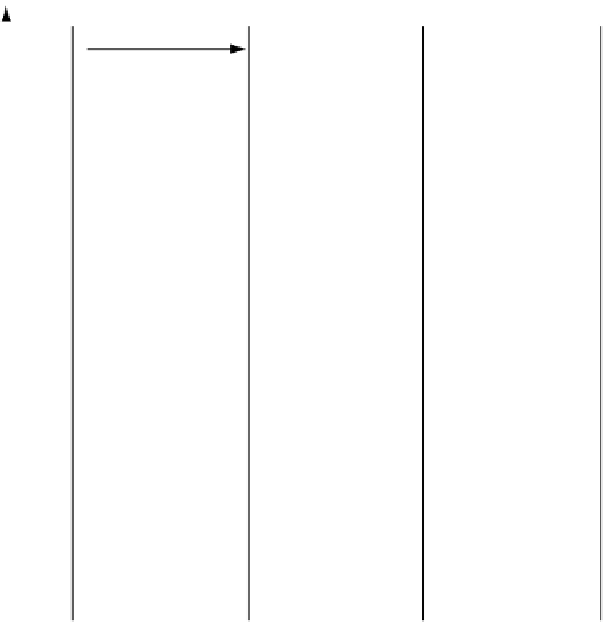

Frequency

WISA frame =

2048

µS

f

DL

012

3

..

..

E

F

f

UL

1

f

UL

4

012

..

..

D

E

F

012

..

..

D

E

F

Time

FIGURE .

WISA TDMA/FDD/FH pattern. Dotted lines connect downlink/uplink slots allocated to one

sensor/actuator. (TX/RX-turnaround time

µs, see Figure .). (From Scheible, G., Dzung,

D.,Endresen,J.,andFrey,J.-E.,

IEEE Ind. Electron. Mag.

, , , . With permission.)

=

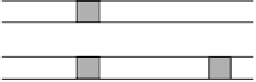

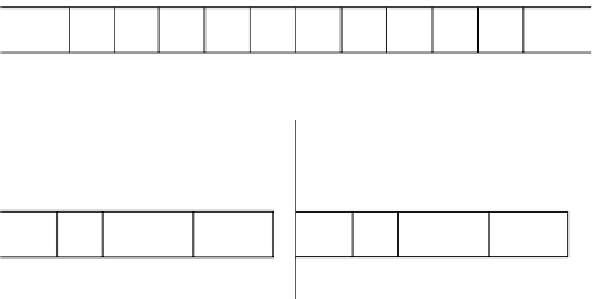

doubleslots

=

Dslot

128 bit

Downlink

Data.

#6.

Cell_

id.

Data.

#1.

Data.

#2.

Data.

#3.

Data.

#4.

Data.

#5.

Data.

#7.

Data.

#8.

Dslot

#.

Preamble

CRC.

Slot

64 bit

Slot

64 bit

Uplink

Pre-

amble.

Pre-

amble.

Cell_

id.

Cell_

id.

Data.

Data.

CRC.

CRC.

FIGURE .

µs. Double slots

may be used on the uplink for higher payload data profiles. (From Scheible, G., Dzung, D., Endresen, J., and Frey, J.-E.,

IEEE Ind. Electron. Mag.

,,,.Withpermission.)

WISA slot format: downlink double slot duration

=

µs, uplink slot duration

=