Hardware Reference

In-Depth Information

gisters. Because only one operation can be in a pipe stage at a time, the control information

can be associated with the register at the head of the stage.

Hazards And Forwarding In Longer Latency Pipelines

There are a number of different aspects to the hazard detection and forwarding for a pipeline

like that shown in

Figure C.35

.

1. Because the divide unit is not fully pipelined, structural hazards can occur. These will need

to be detected and issuing instructions will need to be stalled.

2. Because the instructions have varying running times, the number of register writes re-

quired in a cycle can be larger than 1.

3. Write after write (WAW) hazards are possible, since instructions no longer reach WB in

order. Note that write after read (WAR) hazards are not possible, since the register reads

always occur in ID.

4. Instructions can complete in a different order than they were issued, causing problems

with exceptions; we deal with this in the next subsection.

5. Because of longer latency of operations, stalls for RAW hazards will be more frequent.

The increase in stalls arising from longer operation latencies is fundamentally the same as

that for the integer pipeline. Before describing the new problems that arise in this FP pipeline

and looking at solutions, let's examine the potential impact of RAW hazards.

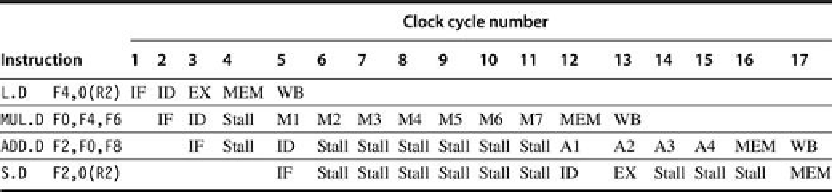

Figure C.37

shows a typical FP code sequence and the resultant stalls. At the end of this section, we'll ex-

amine the performance of this FP pipeline for our SPEC subset.

FIGURE C.37

A typical FP code sequence showing the stalls arising from RAW hazar-

ds

. The longer pipeline substantially raises the frequency of stalls versus the shallower in-

teger pipeline. Each instruction in this sequence is dependent on the previous and proceeds

as soon as data are available, which assumes the pipeline has full bypassing and forwarding.

The

S.D

must be stalled an extra cycle so that its MEM does not conflict with the

ADD.D

. Extra

hardware could easily handle this case.

Now look at the problems arising from writes, described as (2) and (3) in the earlier list. If

we assume that the FP register file has one write port, sequences of FP operations, as well as

an FP load together with FP operations, can cause conflicts for the register write port. Con-

sider the pipeline sequence shown in

Figure C.38

.

In clock cycle 11, all three instructions will

reach WB and want to write the register file. With only a single register file write port, the pro-

cessor must serialize the instruction completion. This single register port represents a struc-

tural hazard. We could increase the number of write ports to solve this, but that solution may

be unatractive since the additional write ports would be used only rarely. This is because the

Search WWH ::

Custom Search