Hardware Reference

In-Depth Information

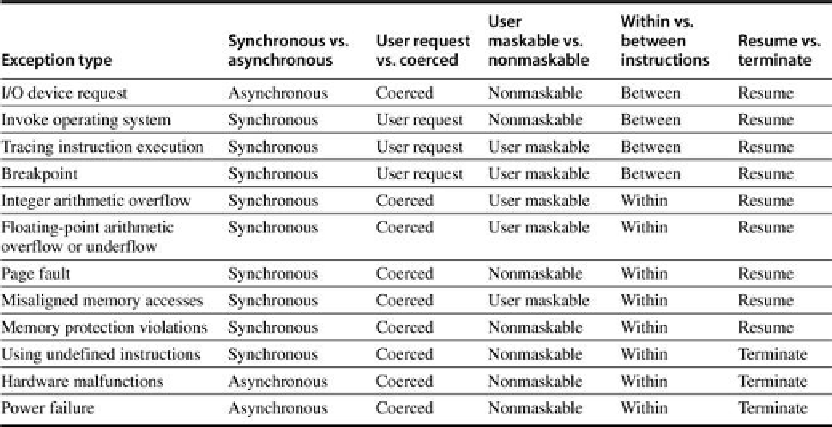

FIGURE C.31

Five categories are used to define what actions are needed for the differ-

ent exception types shown in

Figure C.30

. Exceptions that must allow resumption are

marked as resume, although the software may often choose to terminate the program. Syn-

chronous, coerced exceptions occurring within instructions that can be resumed are the most

difficult to implement. We might expect that memory protection access violations would al-

ways result in termination; however, modern operating systems use memory protection to de-

tect events such as the first attempt to use a page or the first write to a page. Thus, CPUs

should be able to resume after such exceptions.

Stopping and Restarting Execution

As in unpipelined implementations, the most difficult exceptions have two properties: (1) they

occur within instructions (that is, in the middle of the instruction execution corresponding to

EX or MEM pipe stages), and (2) they must be restartable. In our MIPS pipeline, for example,

a virtual memory page fault resulting from a data fetch cannot occur until sometime in the

MEM stage of the instruction. By the time that fault is seen, several other instructions will be

in execution. A page fault must be restartable and requires the intervention of another pro-

cess, such as the operating system. Thus, the pipeline must be safely shut down and the state

saved so that the instruction can be restarted in the correct state. Restarting is usually imple-

mented by saving the PC of the instruction at which to restart. If the restarted instruction is not

a branch, then we will continue to fetch the sequential successors and begin their execution in

the normal fashion. If the restarted instruction is a branch, then we will reevaluate the branch

condition and begin fetching from either the target or the fall-through. When an exception oc-

curs, the pipeline control can take the following steps to save the pipeline state safely:

1. Force a trap instruction into the pipeline on the next IF.

2. Until the trap is taken, turn of all writes for the faulting instruction and for all instructions

that follow in the pipeline; this can be done by placing zeros into the pipeline latches of

all instructions in the pipeline, starting with the instruction that generates the exception,

Search WWH ::

Custom Search