Hardware Reference

In-Depth Information

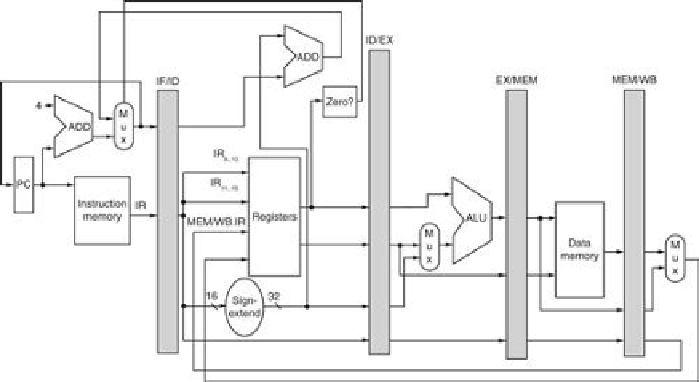

FIGURE C.28

The stall from branch hazards can be reduced by moving the zero test

and branch-target calculation into the ID phase of the pipeline

. Notice that we have made

two important changes, each of which removes 1 cycle from the 3-cycle stall for branches.

The first change is to move both the branch-target address calculation and the branch condi-

tion decision to the ID cycle. The second change is to write the PC of the instruction in the IF

phase, using either the branch-target address computed during ID or the incremented PC

computed during IF. In comparison,

Figure C.22

obtained the branch-target address from the

EX/MEM register and wrote the result during the MEM clock cycle. As mentioned in

Figure

C.22

, the PC can be thought of as a pipeline register (e.g., as part of ID/IF), which is written

with the address of the next instruction at the end of each IF cycle.

Search WWH ::

Custom Search