Hardware Reference

In-Depth Information

pipeline—must continue, since otherwise the hazard will never clear. As a result, no new in-

structions are fetched during the stall. We will see several examples of how pipeline stalls op-

erate in this section—don't worry, they aren't as complex as they might sound!

Performance Of Pipelines With Stalls

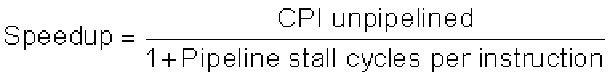

A stall causes the pipeline performance to degrade from the ideal performance. Let's look at

a simple equation for finding the actual speedup from pipelining, starting with the formula

from the previous section:

Pipelining can be thought of as decreasing the CPI or the clock cycle time. Since it is tradi-

tional to use the CPI to compare pipelines, let's start with that assumption. The ideal CPI on a

pipelined processor is almost always 1. Hence, we can compute the pipelined CPI:

If we ignore the cycle time overhead of pipelining and assume that the stages are perfectly

balanced, then the cycle time of the two processors can be equal, leading to

One important simple case is where all instructions take the same number of cycles, which

must also equal the number of pipeline stages (also called the

depth of the pipeline

). In this case,

the unpipelined CPI is equal to the depth of the pipeline, leading to

Search WWH ::

Custom Search