Hardware Reference

In-Depth Information

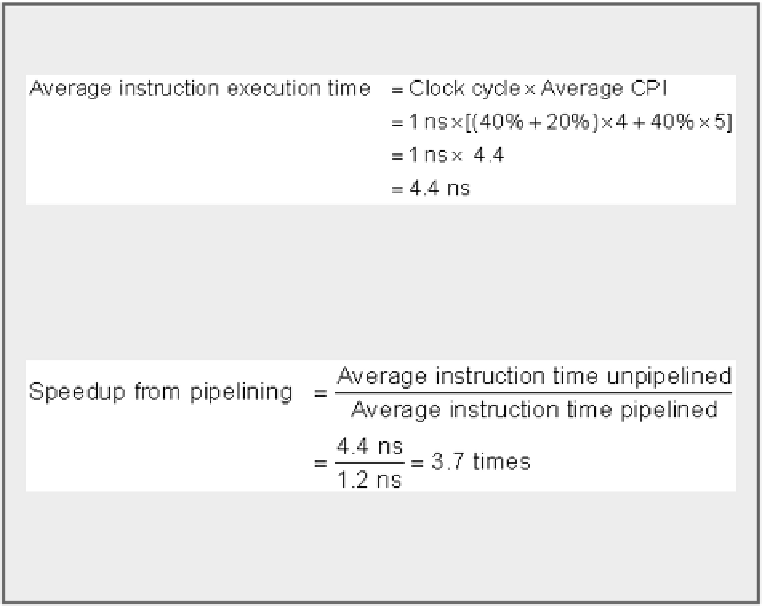

In the pipelined implementation, the clock must run at the speed of the slow-

est stage plus overhead, which will be 1 + 0.2 or 1.2 ns; this is the average in-

struction execution time. Thus, the speedup from pipelining is

The 0.2 ns overhead essentially establishes a limit on the effectiveness of

pipelining. If the overhead is not affected by changes in the clock cycle, Am-

dahl's law tells us that the overhead limits the speedup.

This simple RISC pipeline would function just fine for integer instructions if every instruc-

tion were independent of every other instruction in the pipeline. In reality, instructions in the

pipeline can depend on one another; this is the topic of the next section.

C.2 The Major Hurdle of Pipelining—Pipeline Hazards

There are situations, called

hazards

, that prevent the next instruction in the instruction stream

from executing during its designated clock cycle. Hazards reduce the performance from the

ideal speedup gained by pipelining. There are three classes of hazards:

1.

Structural hazards

arise from resource conflicts when the hardware cannot support all pos-

sible combinations of instructions simultaneously in overlapped execution.

2.

Data hazards

arise when an instruction depends on the results of a previous instruction in a

way that is exposed by the overlapping of instructions in the pipeline.

3.

Control hazards

arise from the pipelining of branches and other instructions that change the

PC.

Hazards in pipelines can make it necessary to

stall

the pipeline. Avoiding a hazard often re-

quires that some instructions in the pipeline be allowed to proceed while others are delayed.

For the pipelines we discuss in this appendix, when an instruction is stalled, all instructions

issued

later

than the stalled instruction—and hence not as far along in the pipeline—are also

stalled. Instructions issued

earlier

than the stalled instruction—and hence farther along in the

Search WWH ::

Custom Search