Hardware Reference

In-Depth Information

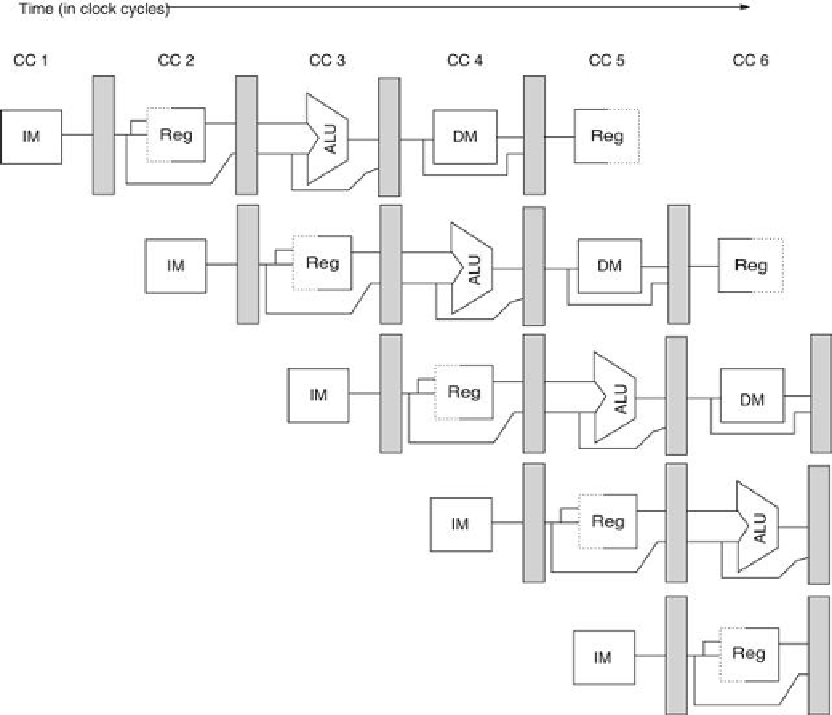

Although it is critical to ensure that instructions in the pipeline do not atempt to use the

hardware resources at the same time, we must also ensure that instructions in different stages

of the pipeline do not interfere with one another. This separation is done by introducing

pipeline registers

between successive stages of the pipeline, so that at the end of a clock cycle

all the results from a given stage are stored into a register that is used as the input to the next

stage on the next clock cycle.

Figure C.3

shows the pipeline drawn with these pipeline re-

gisters.

FIGURE C.3

A pipeline showing the pipeline registers between successive pipeline

stages

. Notice that the registers prevent interference between two different instructions in ad-

jacent stages in the pipeline. The registers also play the critical role of carrying data for a giv-

en instruction from one stage to the other. The edge-triggered property of registers—that is,

that the values change instantaneously on a clock edge—is critical. Otherwise, the data from

one instruction could interfere with the execution of another!

Search WWH ::

Custom Search