Hardware Reference

In-Depth Information

Several general memory hierarchy ideas from

Chapter 1

about caches are analogous to vir-

tual memory, although many of the terms are different.

Page

or

segment

is used for block, and

page fault

or

address fault

is used for miss. With virtual memory, the processor produces

vir-

tual addresses

that are translated by a combination of hardware and software to

physical ad-

dresses

, which access main memory. This process is called

memory mapping

or

address transla-

tion

. Today, the two memory hierarchy levels controlled by virtual memory are DRAMs and

magnetic disks.

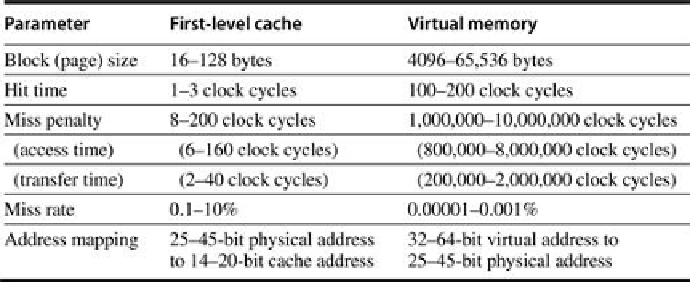

Figure B.20

shows a typical range of memory hierarchy parameters for virtual

memory.

FIGURE B.20

Typical ranges of parameters for caches and virtual memory

. Virtual

memory parameters represent increases of 10 to 1,000,000 times over cache para-meters.

Normally, first-level caches contain at most 1 MB of data, whereas physical memory contains

256 MB to 1 TB.

There are further differences between caches and virtual memory beyond those quantitative

ones mentioned in

Figure B.20

:

■ Replacement on cache misses is primarily controlled by hardware, while virtual memory

replacement is primarily controlled by the operating system. The longer miss penalty

means it's more important to make a good decision, so the operating system can be in-

volved and take time deciding what to replace.

■ The size of the processor address determines the size of virtual memory, but the cache size

is independent of the processor address size.

■ In addition to acting as the lower-level backing store for main memory in the hierarchy,

secondary storage is also used for the file system. In fact, the file system occupies most of

secondary storage. It is not normally in the address space.

Virtual memory also encompasses several related techniques. Virtual memory systems can

be categorized into two classes: those with fixed-size blocks, called

pages

, and those with

variable-size blocks, called

segments

. Pages are typically fixed at 4096 to 8192 bytes, while seg-

ment size varies. The largest segment supported on any processor ranges from 2

16

bytes up to

vide code and data.

Search WWH ::

Custom Search