Hardware Reference

In-Depth Information

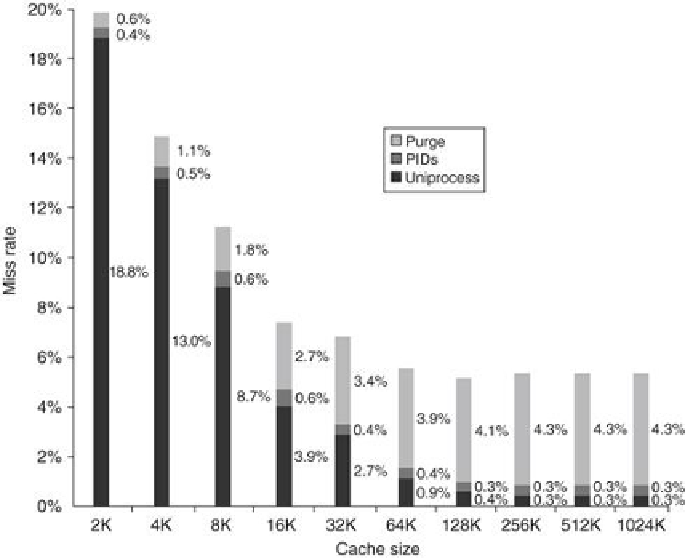

FIGURE B.16

Miss rate versus virtually addressed cache size of a program measured

three ways: without process switches (uniprocess), with process switches using a

process-identifier tag (PID), and with process switches but without PIDs (purge)

. PIDs

increase the uniprocess absolute miss rate by 0.3% to 0.6% and save 0.6% to 4.3% over pur-

ging. Agarwal [1987] collected these statistics for the Ultrix operating system running on a

VAX, assuming direct-mapped caches with a block size of 16 bytes. Note that the miss rate

goes up from 128K to 256K. Such nonintuitive behavior can occur in caches because chan-

ging size changes the mapping of memory blocks onto cache blocks, which can change the

conflict miss rate.

A third reason why virtual caches are not more popular is that operating systems and user

programs may use two different virtual addresses for the same physical address. These du-

plicate addresses, called

synonyms

or

aliases

, could result in two copies of the same data in a

virtual cache; if one is modified, the other will have the wrong value. With a physical cache

this wouldn't happen, since the accesses would first be translated to the same physical cache

block.

Hardware solutions to the synonym problem, called

antialiasing

, guarantee every cache

block a unique physical address. For example, the AMD Opteron uses a 64 KB instruction

cache with a 4 KB page and two-way set associativity; hence, the hardware must handle aliases

involved with the three virtual address bits in the set index. It avoids aliases by simply check-

ing all eight possible locations on a miss—two blocks in each of four sets—to be sure that none

matches the physical address of the data being fetched. If one is found, it is invalidated, so

when the new data are loaded into the cache their physical address is guaranteed to be unique.

Search WWH ::

Custom Search