Hardware Reference

In-Depth Information

where

hit time

is the time to hit in the cache; we have seen the other two terms before.

The components of average access time can be measured either in absolute time—say, 0.25 to

1.0 nanoseconds on a hit—or in the number of clock cycles that the processor waits for the

memory—such as a miss penalty of 150 to 200 clock cycles. Remember that average memory

access time is still an indirect measure of performance; although it is a beter measure than

miss rate, it is not a substitute for execution time.

This formula can help us decide between split caches and a unified cache.

Example

Which has the lower miss rate: a 16 KB instruction cache with a 16 KB data cache

or a 32 KB unified cache? Use the miss rates in

Figure B.6

to help calculate the

correct answer, assuming 36% of the instructions are data transfer instructions.

Assume a hit takes 1 clock cycle and the miss penalty is 100 clock cycles. A load

or store hit takes 1 extra clock cycle on a unified cache if there is only one cache

port to satisfy two simultaneous requests. Using the pipelining terminology of

memory access time in each case? Assume write-through caches with a write

buffer and ignore stalls due to the write buffer.

Answer

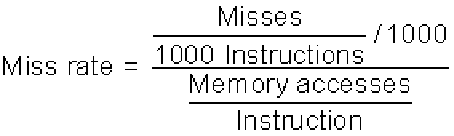

First let's convert misses per 1000 instructions into miss rates. Solving the gen-

eral formula from above, the miss rate is

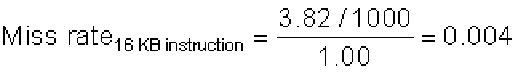

Since every instruction access has exactly one memory access to fetch the in-

struction, the instruction miss rate is

Since 36% of the instructions are data transfers, the data miss rate is

Search WWH ::

Custom Search