Hardware Reference

In-Depth Information

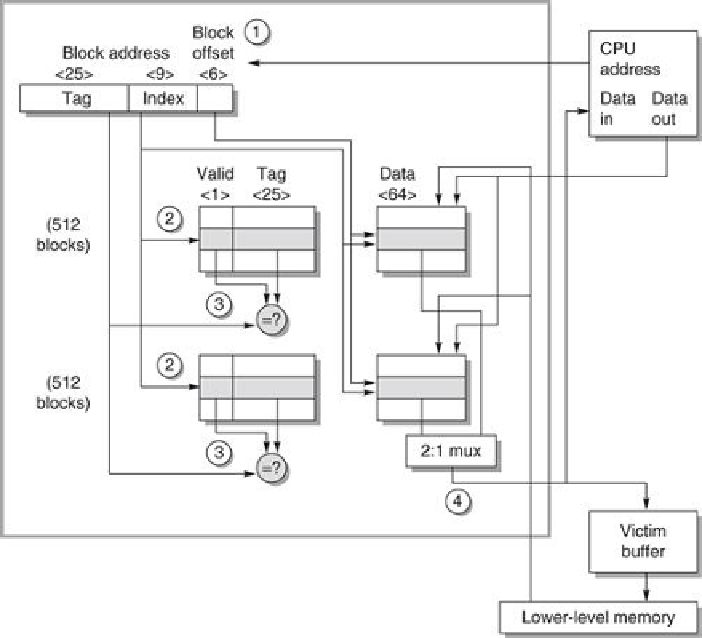

FIGURE B.5

The organization of the data cache in the Opteron microprocessor

. The 64

KB cache is two-way set associative with 64-byte blocks. The 9-bit index selects among 512

sets. The four steps of a read hit, shown as circled numbers in order of occurrence, label this

organization. Three bits of the block offset join the index to supply the RAM address to select

the proper 8 bytes. Thus, the cache holds two groups of 4096 64-bit words, with each group

containing half of the 512 sets. Although not exercised in this example, the line from lower-

level memory to the cache is used on a miss to load the cache. The size of address leaving

the processor is 40 bits because it is a physical address and not a virtual address.

Figure B.24

on page B-47 explains how the Opteron maps from virtual to physical for a cache access.

Let's trace a cache hit through the steps of a hit as labeled in

Figure B.5

.

(The four steps are

shown as circled numbers.) As described in

Section B.5

, the Opteron presents a 48-bit virtual

address to the cache for tag comparison, which is simultaneously translated into a 40-bit phys-

ical address.

The reason Opteron doesn't use all 64 bits of virtual address is that its designers don't think

anyone needs that big of a virtual address space yet, and the smaller size simplifies the Opter-

on virtual address mapping. The designers plan to grow the virtual address in future micro-

processors.

The physical address coming into the cache is divided into two fields: the 34-bit block ad-

dress and the 6-bit block offset (64 = 2

6

and 34 + 6 = 40). The block address is further divided

into an address tag and cache index. Step 1 shows this division.

Search WWH ::

Custom Search