Hardware Reference

In-Depth Information

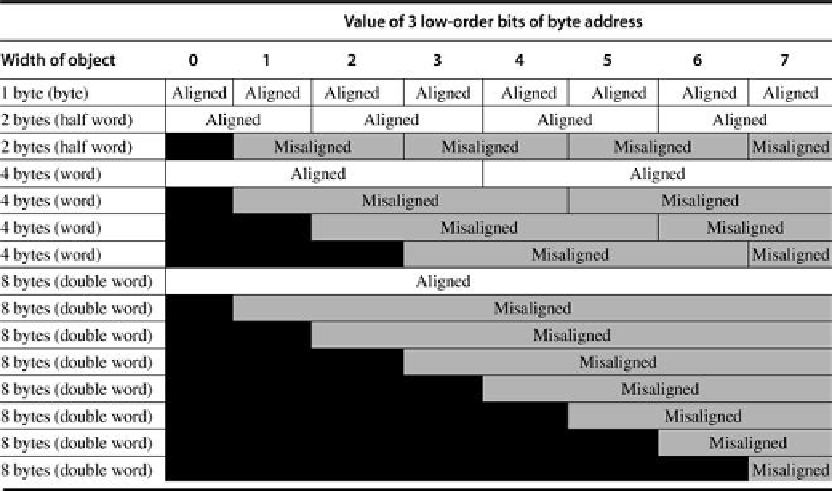

FIGURE A.5

Aligned and misaligned addresses of byte, half-word, word, and double-

word objects for byte-addressed computers

. For each misaligned example some objects

require two memory accesses to complete. Every aligned object can always complete in one

memory access, as long as the memory is as wide as the object. The figure shows the

memory organized as 8 bytes wide. The byte offsets that label the columns specify the low-or-

der 3 bits of the address.

Why would someone design a computer with alignment restrictions? Misalignment causes

hardware complications, since the memory is typically aligned on a multiple of a word or

double-word boundary. A misaligned memory access may, therefore, take multiple aligned

memory references. Thus, even in computers that allow misaligned access, programs with

aligned accesses run faster.

Even if data are aligned, supporting byte, half-word, and word accesses requires an align-

ment network to align bytes, half words, and words in 64-bit registers. For example, in

Figure

will need to shift right 3 bytes to align the byte to the proper place in a 64-bit register. Depend-

ing on the instruction, the computer may also need to sign-extend the quantity. Stores are easy:

Only the addressed bytes in memory may be altered. On some computers a byte, half-word,

and word operation does not affect the upper portion of a register. Although all the computers

discussed in this topic permit byte, half-word, and word accesses to memory, only the IBM

360/370, Intel 80×86, and VAX support ALU operations on register operands narrower than

the full width.

Now that we have discussed alternative interpretations of memory addresses, we can dis-

cuss the ways addresses are specified by instructions, called

addressing modes

.

Search WWH ::

Custom Search