Hardware Reference

In-Depth Information

dressing, where the branch address is specified by an address field that is added to the PC.

There are some small differences. MIPS conditional branches (

BE

,

BNE

, etc.) test the contents

of registers, while the 80x86 and ARM branches test condition code bits set as side effects of

arithmetic/logic operations. The ARM and MIPS procedure call places the return address

in a register, while the 80x86 call (

CALLF

) places the return address on a stack in memory.

7.

Encoding an ISA

—There are two basic choices on encoding:

fixed length

and v

ariable length

.

All ARM and MIPS instructions are 32 bits long, which simplifies instruction decoding.

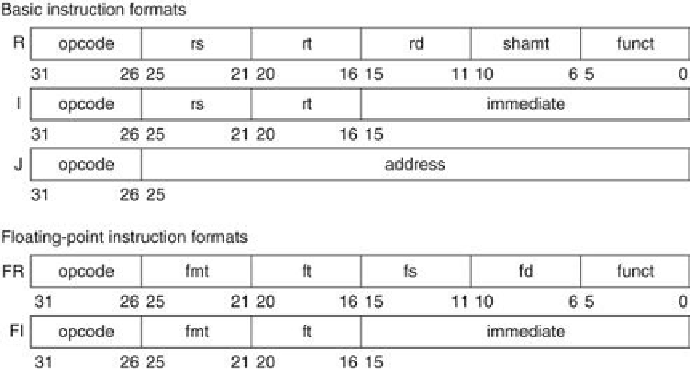

Figure 1.6

shows the MIPS instruction formats. The 80x86 encoding is variable length, ran-

ging from 1 to 18 bytes. Variable-length instructions can take less space than ixed-length

instructions, so a program compiled for the 80x86 is usually smaller than the same pro-

gram compiled for MIPS. Note that choices mentioned above will affect how the instruc-

tions are encoded into a binary representation. For example, the number of registers and

the number of addressing modes both have a significant impact on the size of instructions,

as the register field and addressing mode field can appear many times in a single instruc-

tion. (Note that ARM and MIPS later offered extensions to offer 16-bit length instructions

so as to reduce program size, called Thumb or Thumb-2 and MIPS16, respectively.)

FIGURE 1.6

MIPS64 instruction set architecture formats

. All instructions are 32 bits long.

The R format is for integer register-to-register operations, such as DADDU, DSUBU, and so

on. The I format is for data transfers, branches, and immediate instructions, such as LD, SD,

BEQZ, and DADDIs. The J format is for jumps, the FR format for floating-point operations,

and the FI format for floating-point branches.

The other challenges facing the computer architect beyond ISA design are particularly acute

at the present, when the differences among instruction sets are small and when there are dis-

tinct application areas. Therefore, starting with the last edition, the bulk of instruction set ma-

terial beyond this quick review is found in the appendices (see

Appendices A

and K).

We use a subset of MIPS64 as the example ISA in this topic because it is both the dominant

ISA for networking and it is an elegant example of the RISC architectures mentioned earlier,

of which ARM (Advanced RISC Machine) is the most popular example. ARM processors were

Search WWH ::

Custom Search