Hardware Reference

In-Depth Information

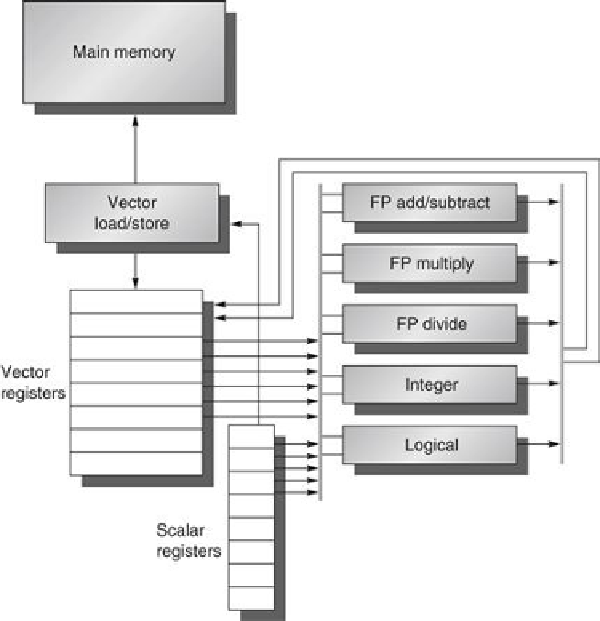

FIGURE 4.2

The basic structure of a vector architecture, VMIPS

. This processor has a

scalar architecture just like MIPS. There are also eight 64-element vector registers, and all the

functional units are vector functional units. This chapter defines special vector instructions for

both arithmetic and memory accesses. The figure shows vector units for logical and integer

operations so that VMIPS looks like a standard vector processor that usually includes these

units; however, we will not be discussing these units. The vector and scalar registers have a

significant number of read and write ports to allow multiple simultaneous vector operations. A

set of crossbar switches (thick gray lines) connects these ports to the inputs and outputs of

the vector functional units.

The primary components of the instruction set architecture of VMIPS are the following:

■

Vector registers

—Each vector register is a fixed-length bank holding a single vector. VMIPS

has eight vector registers, and each vector register holds 64 elements, each 64 bits wide.

The vector register file needs to provide enough ports to feed all the vector functional units.

These ports will allow a high degree of overlap among vector operations to different vector

registers. The read and write ports, which total at least 16 read ports and 8 write ports, are

connected to the functional unit inputs or outputs by a pair of crossbar switches.

■

Vector functional units

—Each unit is fully pipelined, and it can start a new operation on

every clock cycle. A control unit is needed to detect hazards, both structural hazards for

functional units and data hazards on register accesses.

Figure 4.2

shows that VMIPS has

ive functional units. For simplicity, we focus exclusively on the floating-point functional

units.

Search WWH ::

Custom Search