Hardware Reference

In-Depth Information

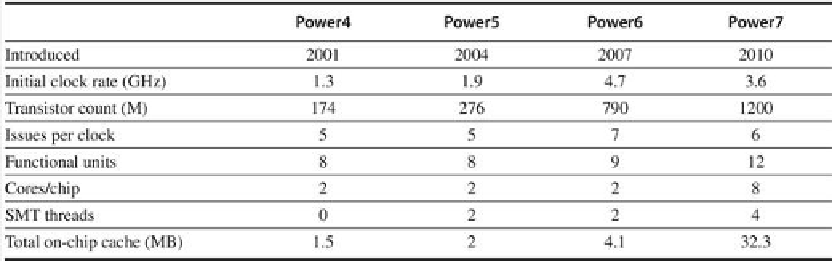

FIGURE 3.47

Characteristics of four IBM Power processors

. All except the Power6 were

dynamically scheduled, which is static, and in-order, and all the processors support two load/

store pipelines. The Power6 has the same functional units as the Power5 except for a decimal

unit. Power7 uses DRAM for the L3 cache.

3.16 Historical Perspective and References

Section L.5 (available online) features a discussion on the development of pipelining and

instruction-level parallelism. We provide numerous references for further reading and explor-

ation of these topics. Section L.5 covers both Chapter 3 and Appendix H.

Case Studies and Exercises by Jason D. Bakos and

Robert P. Colwell

Case Study: Exploring The Impact Of Microarchitectural

Techniques

Concepts illustrated by this case study

■ Basic Instruction Scheduling, Reordering, Dispatch

■ Multiple Issue and Hazards

■ Register Renaming

■ Out-of-Order and Speculative Execution

■ Where to Spend Out-of-Order Resources

You are tasked with designing a new processor microarchitecture, and you are trying to ig-

ure out how best to allocate your hardware resources. Which of the hardware and software

techniques you learned in Chapter 3 should you apply? You have a list of latencies for the

functional units and for memory, as well as some representative code. Your boss has been

somewhat vague about the performance requirements of your new design, but you know from

experience that, all else being equal, faster is usually beter. Start with the basics.

Figure 3.48

provides a sequence of instructions and list of latencies.

Search WWH ::

Custom Search