Hardware Reference

In-Depth Information

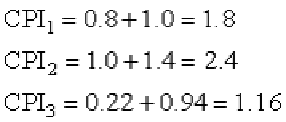

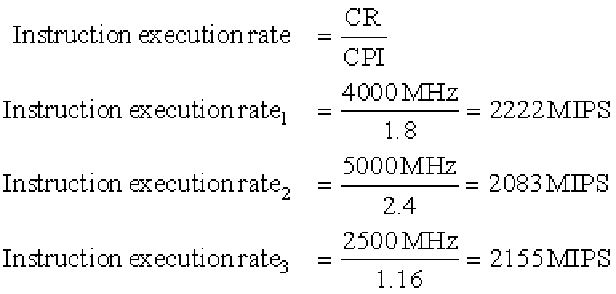

Since this is the same architecture, we can compare instruction execution rates

in millions of instructions per second (MIPS) to determine relative performance:

In this example, the simple two-issue static superscalar looks best. In practice,

performance depends on both the CPI and clock rate assumptions.

Beyond The Limits Of This Study

Like any limit study, the study we have examined in this section has its own limitations. We

divide these into two classes: limitations that arise even for the perfect speculative processor,

and limitations that arise for one or more realistic models. Of course, all the limitations in the

first class apply to the second. The most important limitations that apply even to the perfect

model are

1.

WAW and WAR hazards through memory

—The study eliminated WAW and WAR hazards

through register renaming, but not in memory usage. Although at first glance it might ap-

pear that such circumstances are rare (especially WAW hazards), they arise due to the all

location of stack frames. A called procedure reuses the memory locations of a previous

procedure on the stack, and this can lead to WAW and WAR hazards that are unnecessarily

limiting.

Austin and Sohi [1992]

examined this issue.

2.

Unnecessary dependences

—With infinite numbers of registers, all but true register data de-

pendences are removed. There are, however, dependences arising from either recurrences

or code generation conventions that introduce unnecessary true data dependences. One

example of these is the dependence on the control variable in a simple for loop. Since the

Search WWH ::

Custom Search