Hardware Reference

In-Depth Information

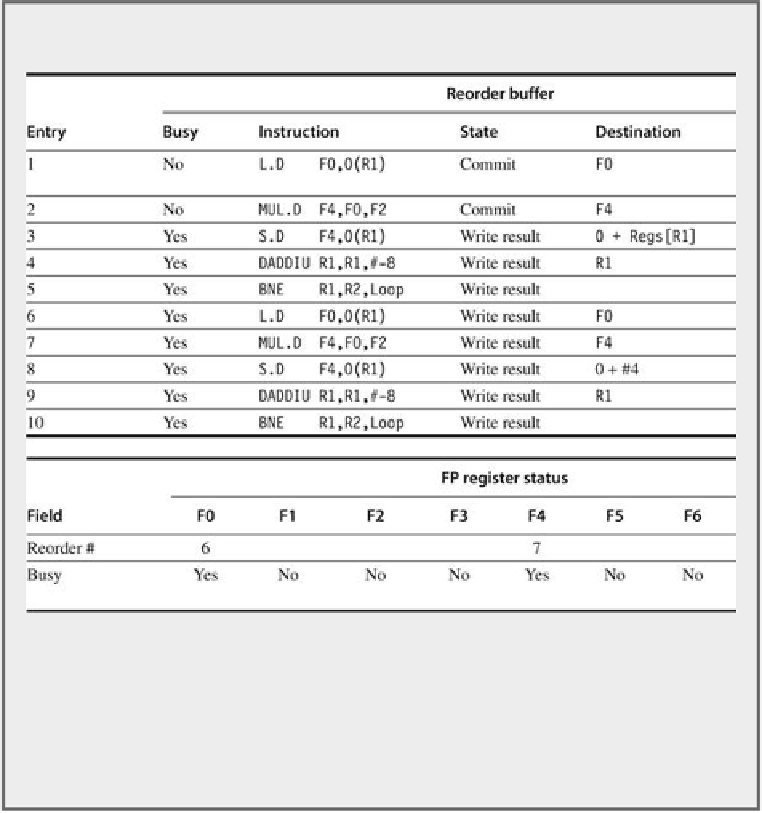

FIGURE 3.13

Only the

L.D

and

MUL.D

instructions have committed, al-

though all the others have completed execution

. Hence, no reservation sta-

tions are busy and none is shown. The remaining instructions will be commit-

ted as quickly as possible. The first two reorder buffers are empty, but are

shown for completeness.

Because neither the register values nor any memory values are actually writen until an

instruction commits, the processor can easily undo its speculative actions when a branch is

The instructions prior to the branch will simply commit when each reaches the head of the

ROB; when the branch reaches the head of that buffer, the buffer is simply cleared and the

processor begins fetching instructions from the other path.

In practice, processors that speculate try to recover as early as possible after a branch is mis-

predicted. This recovery can be done by clearing the ROB for all entries that appear after the

mispredicted branch, allowing those that are before the branch in the ROB to continue, and

restarting the fetch at the correct branch successor. In speculative processors, performance is

more sensitive to the branch prediction, since the impact of a misprediction will be higher.

Search WWH ::

Custom Search