Hardware Reference

In-Depth Information

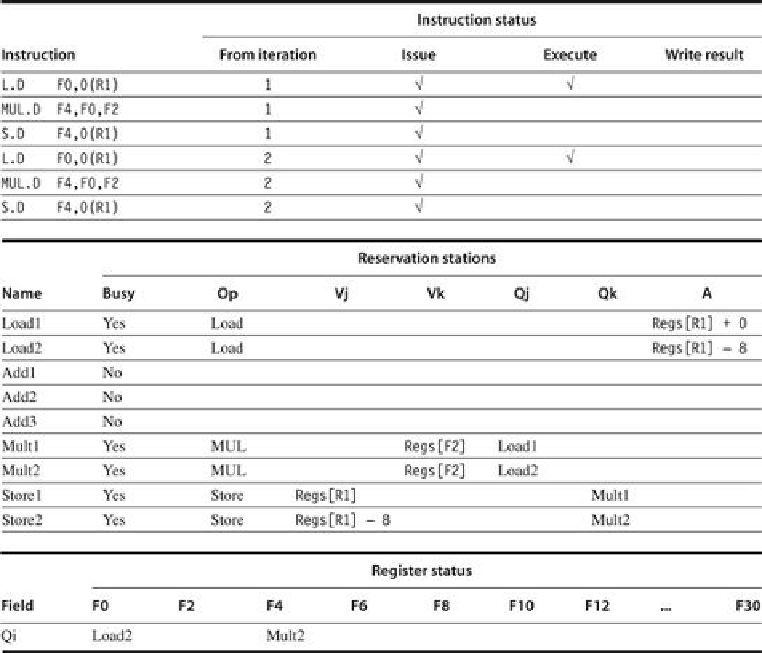

FIGURE 3.10

Two active iterations of the loop with no instruction yet completed

. En-

tries in the multiplier reservation stations indicate that the outstanding loads are the sources.

The store reservation stations indicate that the multiply destination is the source of the value

to store.

A load and a store can safely be done out of order, provided they access different addresses.

If a load and a store access the same address, then either

■ The load is before the store in program order and interchanging them results in a WAR

hazard, or

■ The store is before the load in program order and interchanging them results in a RAW

hazard.

Similarly, interchanging two stores to the same address results in a WAW hazard.

Hence, to determine if a load can be executed at a given time, the processor can check

whether any uncompleted store that precedes the load in program order shares the same data

memory address as the load. Similarly, a store must wait until there are no unexecuted loads

or stores that are earlier in program order and share the same data memory address. We con-

sider a method to eliminate this restriction in

Section 3.9

.

To detect such hazards, the processor must have computed the data memory address asso-

ciated with any earlier memory operation. A simple, but not necessarily optimal, way to guar-

antee that the processor has all such addresses is to perform the effective address calculations

Search WWH ::

Custom Search