Hardware Reference

In-Depth Information

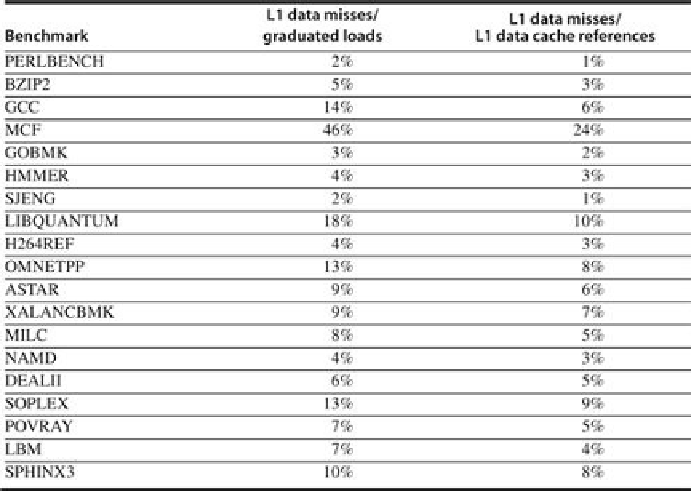

FIGURE 2.23

The primary data cache misses are shown versus all loads that complete

and all references (which includes speculative and prefetch requests)

.

With L1 data cache miss rates running 5% to 10%, and sometimes higher, the importance

of the L2 and L3 caches should be obvious.

Figure 2.24

shows the miss rates of the L2 and L3

caches versus the number of L1 references (and

Figure 2.25

shows the data in tabular form).

Since the cost for a miss to memory is over 100 cycles and the average data miss rate in L2

is 4%, L3 is obviously critical. Without L3 and assuming about half the instructions are loads

for stores, L2 cache misses could add two cycles per instruction to the CPI! In comparison, the

average L3 data miss rate of 1% is still significant but four times lower than the L2 miss rate

and six times less than the L1 miss rate. In the next chapter, we will examine the relationship

between the i7 CPI and cache misses, as well as other pipeline effects.

Search WWH ::

Custom Search