Hardware Reference

In-Depth Information

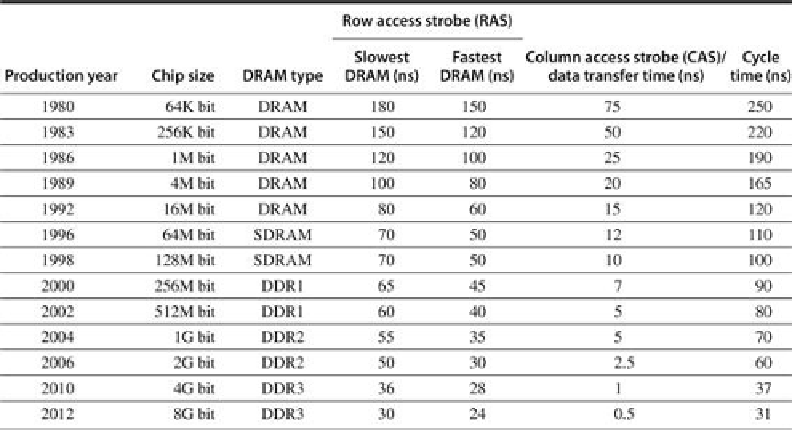

improvement in row access time, which is related to latency, of about 5% per year. The CAS

or data transfer time, which is related to bandwidth, is growing at more than twice that rate.

FIGURE 2.13

Times of fast and slow DRAMs vary with each generation

. (Cycle time is

defined on page 97.) Performance improvement of row access time is about 5% per year. The

improvement by a factor of 2 in column access in 1986 accompanied the switch from NMOS

DRAMs to CMOS DRAMs. The introduction of various burst transfer modes in the mid-1990s

and SDRAMs in the late 1990s has significantly complicated the calculation of access time for

blocks of data; we discuss this later in this section when we talk about SDRAM access time

and power. The DDR4 designs are due for introduction in mid- to late 2012. We discuss these

various forms of DRAMs in the next few pages.

Although we have been talking about individual chips, DRAMs are commonly sold on

small boards called

dual inline memory modules

(DIMMs). DIMMs typically contain 4 to 16

DRAMs, and they are normally organized to be 8 bytes wide (+ ECC) for desktop and server

systems.

In addition to the DIMM packaging and the new interfaces to improve the data transfer

time, discussed in the following subsections, the biggest change to DRAMs has been a slowing

down in capacity growth. DRAMs obeyed Moore's law for 20 years, bringing out a new chip

with four times the capacity every three years. Due to the manufacturing challenges of a

single-bit DRAM, new chips only double capacity every two years since 1998. In 2006, the pace

slowed further, with the four years from 2006 to 2010 seeing only a doubling of capacity.

Improving Memory Performance Inside A DRAM Chip

As Moore's law continues to supply more transistors and as the processor-memory gap in-

creases pressure on memory performance, the ideas of the previous section have made their

way inside the DRAM chip. Generally, innovation has led to greater bandwidth, sometimes

Search WWH ::

Custom Search