Image Processing Reference

In-Depth Information

Although the spectral trigger is being developed for the future and for a single detection

channel (a single PMT), the DCT trigger in the Auger surface detector has been tested in a

2-fold coincidences of any 3 PMTs, to be close as possible for a comparison of the results with

the standard Auger data.

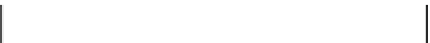

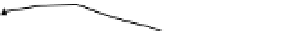

Rates for Occ = 6

Rates for Occ = 7

0.20 1.00

0.20 1.14

0.20

0.20 1.00

0.25 1.00

350

120

0.20 1.30

0.20 1.50

0.25 1.00

1.30

0.30 1.00

0.20 1.14

0.25 1.14

300

100

250

0.25 1.14

0.25 1.30

0.25 1.50

80

0.30 1.14

0.20 1.30

0.25 1.30

80

200

60

150

150

0.30 1.00

0.30 1.14

0.30 1.30

0.30 1.30

0.20 1.50

0.25 1.50

40

100

20

20

50

0.30 1.50

0.30 1.50

0

0

veto

ADC

veto

ADC

ADC counts

t

0

10

20

30

40

50

60

70

80

ADC counts

t

0

10

20

30

40

50

60

70

80

Fig. 14. Rates for various acceptance lanes (from 0.20 - 1.00 till 0.30 - 1.50) and the veto

threshold (0 - 80 ADC-counts) for the Occupancy = 6 (left) and 7 (right), respectively. Due to

a possible saturation of a transmission channel, the rate of the spectral trigger should not

exceed ca. 40 Hz.

Fig. 14 show the trigger rate for the Occupancy = 6 and 7, respectively. The T1 trigger rate

is calibrated to ca. 100 Hz. Generally, the trigger rate for Occ = 6 is too high. In order not to

saturate the microcontroller and the transmission chain the total (standard Auger + spectral)

trigger rate should not exceed 150 Hz. This gives max. 40 - 50 Hz for the spectral trigger

only. The Occupancy = 7 with a range of attenuation factors limited to

= (0.20 - 1.14) gives a

trigger range on the reasonable level. The Occupancy = 8 reduces the trigger rate below 1 Hz

and seems to be too restrictive. The FPGA contains internal counters counting the trigger rate

and a contribution of DCT sub-triggers to the final trigger. The required trigger rate range can

be set remotely from the Central Data Acquisition System (CDAS). The FPGA automatically

tunes the veto threshold to get the required trigger rate. If the veto threshold is above 60

ADC-counts (ca. 1.2 VEM) the acceptance lane is modified. The attenuation factor

β

from

the left side of the range is increased/decreased in the range of (0.20 - 0.40) by the fixed right

boundary

β

= 1.3.

Fig. 15 show three calibration processes, when either initial parameters has been set ideally (B)

or they have to be tuned to get required trigger rate (A and C). The tuning process typically

does not exceed 3 minutes. In contrary to the standard Auger tuning procedure, when the

thresholds for the Threshold trigger are calculated by the external microcontroller located on

the Unified Board (UB), the thresholds for the acceptance DCT lane are initially calculated

and next stored in the ROM inside the FPGA and they are only multiplexed. This allows a

full autonomous FPGA calibration process without a support by any external microcontroller.

The new Front-End Board samples analog signals with 80 MHz. Data is written via a left port

in the dual-port RAM. Stored data are next read via the right port with 40 MHz. The new

board is seen by the rest of electronics as the standard one. Only a additional flag informs the

system on the type of the trigger. Internal FPGA counters allow counting a contribution of

the DCT coefficients to the final spectral trigger. Fig. 15d shows a relative contribution of the

DCT coefficients for the Shape_A. The contribution of the

X

5

and

X

9

is a little bit lower than

the rest ones. For the

X

9

the acceptance lane (compare Fig. 13A) is relatively narrow, so the

lower contribution is not strange.

X

5

is probably more sensitive on signal noise and possible

signal distortions. The graph A (Fig. 15) shows a process when the trigger rate is initially too

β