Image Processing Reference

In-Depth Information

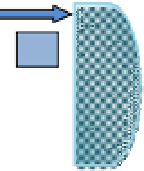

indices may be taken from the last 16 shift register nodes according to the Fig. 11. The samples

with higher indices correspond to the exponentially attenuated tail and the analysis of the tail

is lest critical than the rising edge, where samples are analyzed with a full speed.

x

16

x

15

x

14

x

13

x

12

x

11

x

10

x

9

x

23

x

22

x

21

x

20

x

19

x

18

x

17

DCT + sub-trigger routines

1

2

3

veto threshold

cmp

χ

χ

χ

veto

x

8

x

7

x

6

x

5

x

4

x

3

x

2

x

1

x

0

Final

spectral

trigger

DCT + sub-trigger routines

ɻ

-1

A

N

D

ɻ

0

ɻ

0'

Thresholds for the jump control

MUX

ɻ

1

ɻ

1'

ɻ

1''

Thresholds for investigating the

exponential attenuation

Fig. 11. A scheme of the final spectral trigger. The shift register presented here has an

extended length = 24 stages to cover longer time window. However, for a sampling

frequencies

f

s

≤

150 ns the window is wide enough for an

analysis of horizontal showers. If signal shifted in the register chain matches the expected

patterns for 4 consecutive time bins i.e. corresponding to ADC shapes in Fig. 3 (1st row, 3

first graphs. The 4th pattern is exactly the same as the 3rd one. The amplitude of the signal

decreases, but the DCT coefficients remain the same (still an exponential attenuation).

100 MHz 16 stages and T

≥

3 DCT trigger "engines" have been successfully merged with the Auger code working with 100

MHz sampling. The final code utilizes only 38gives an opportunity to add new, sophisticated

algorithms. The slack reported by the compiler corresponds to a maximal sampling frequency

112 MHz, which gives a sufficient safety margin for a stable operation of the system. For

sufficiently high amplitudes of the ADC samples the Threshold trigger will be generated

32 clock cycles earlier than the spectral trigger (24 clock cycles of propagation in the shift

registers + 8 clock cycles of performance in the DCT chain). If the Threshold trigger has

been already generated, the next triggers are inhibited for 768 time bins necessary to fulfill

memory buffers (see Fig. 7 in (Szadkowski, 2005a)). Because the Threshold trigger (sensitive

to bigger signals) has a higher priority than the spectral trigger, ADC samples will not be

delayed for the Threshold trigger in order to synchronize it with the spectral one. The system

uses 10-bit resolution (standard Auger one). A compilation for the 12-bit resolution for the

current chip EP3C40F324I7 failed, due to a lack of the DSP blocks. 12-bit system requires

bigger chip EP3C55. The slack times are on the same level as for EP3C40. All pipeline routines

shown in Fig. 8 are implemented in a direct mode (no pipeline mode - like i.e. in the 2nd

generation of the FEB based on the ACEX family (see Fig. 2 in (Szadkowski, 2005a)) or for the

FFT implementation in the Cyclone family (Fig. 2 in (Szadkowski, 2005b)). So, a performance