Image Processing Reference

In-Depth Information

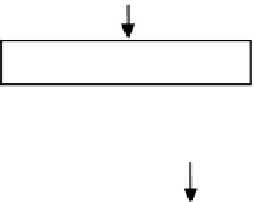

Therefore, these six operands should be added using a modulo (2

4

n

-1) multi-operand adder

which can be realised by four carry-save adders (CSAs) with end-around carry (EAC)

followed by a modulo (2

4

n

-1) carry propagate adder (CPA) with EAC (Piestrak, 1994, 1995).

The hardware architecture of the resulted converter is shown in Fig. 1.

x

x

x

x

3

2

4

Operand Preparation Unit

4

n

-bit CSA with EAC

4

n

-bit CSA with EAC

4

n

-bit CSA with EAC

4

n

-bit CSA with EAC

4

n

-bit CPA with EAC

x

Z

X

Fig. 1. The converter for moduli set {2

n

-1, 2

n

, 2

n

+1, 2

2n

+1} (Cao et al., 2003)

4. Reverse converter for the moduli set {2

n

-1, 2

n

+1, 2

2

n

, 2

2n

+1}

The moduli set {2

n

-1, 2

n

+1, 2

2n

, 2

2n

+1} has been recently introduced by (Molahosseini et al.,

2010) to provide large dyamic range (6

n

-bit), and high-speed reverse converter. Similar to

(Cao et al., 2003), the New CRT-I has used to design converter but with different moduli

order, i.e. {2

2n

, 2

2n

+1, 2

n

+1, 2

n

-1}. Therefore, by letting

P

1

=2

2n

,

P

2

=2

2n

+1,

P

3

=2

n

+1 and

P

4

=2

n

-1,

and putting the multiplicative inverses in the New CRT-I formulas (11)-(14), we have the

following main conversion equation (Molahosseini et al., 2010).

2

n

2

n

1

2

n

2(

xx

)2

(2

1 (

xx

)

2

n

2

1

3

2

Xx

2

(34)

1

2

n

22

(2

n

1)(2

n

1)(

xx

)

4

3

4

n

21

Simplification of this equation can be done as follows

Xx

2

2

n

Z

(35)

1

Where

Zv v v v v

(36)

1

2

31

32

4

21

4

n