Image Processing Reference

In-Depth Information

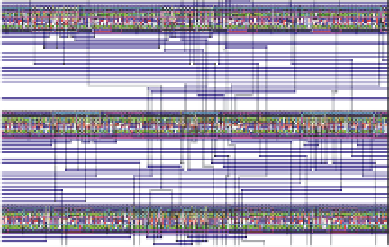

The quantitative measures of the image enhancement/reconstruction performance achieved

with the particular employed DEDR-RSF and DEDR-RASF techniques, evaluated via IOSNR

metric (26), are reported in Table 1 and Fig. 4.

RSF Method RASF Method

IOSNR

[dB]

IOSNR

[dB]

5 4.36 7.94

10 6.92 9.75

15 7.67 11.36

20 9.48 12.72

Table 1. Comparative table of image enhancenment with DEDR-related RSF and RASF

algorithms

SNR

[dB]

From the RS performance analysis with the VLSI-FPGA platform of Fig.4 and Table 1, one

may deduce that the RASF method over-performs the robust non-adaptive RSF in all

simulated scenarios.

4.3 MPPA analysis

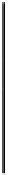

The matrix-vector multiplier chip and all of modules of the MPPA co-processor architecture

were designed by gate-level description. As already mentioned, the chip was designed

using a Standard Cell library in a 0.6µm CMOS process (Weste & D. Harris, 2004), (Rabaey

et al., 2003). The resulting integrated circuit core has dimensions of

7.4

mm

x

3.5

mm

. The

total gate count is about 32K using approximately 185K transistors. The 72-pin chip will be

packaged in an 80 LD CQFP package and can operate both at 5 V and 3 V. The chip is

illustrated in Fig. 5.

Fig. 5. Layout scheme of the proposed MPPA architecture