Graphics Programs Reference

In-Depth Information

p

act1

p

act2

T

req1

λ

1

λ

2

T

req2

p

idle

p

req1

p

req2

T

str1

α

1

α

2

T

str2

p

acc1

p

acc2

T

end1

µ

1

µ

2

T

end2

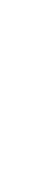

Figure 6.1: The SPN description of shared memory system

common shared memory. The net comprises seven places and six timed tran-

sitions with single-server semantics; for convenience the SPN is depicted in

Fig.

Starting from the initial marking shown in Fig.

6.1,

in which the two pro-

cessors are both in a locally active state (p

act1

+ p

act2

+ p

idle

), a possible

evolution of the SPN marking that focuses on the processing cycle of pro-

cessor 1, may be the following. Processor 1 works locally for an exponentially

distributed random amount of time with average 1/λ

1

, and then requests

an access to the common memory. Transition T

req1

fires, and the token con-

tained in p

act1

is removed while a token is added in p

req1

. Since the common

memory is available (place p

idle

is marked), the acquisition of the memory

starts immediately and takes an average of 1/α

1

units of time to complete;

this is represented by the firing of transition T

str1

whose associated delay

has a negative-exponential distribution with rate α

1

; when transition T

str1

fires, one token is removed from place p

req1

and another token is deposited

into place p

acc1

, where it stays for the entire time required by the first pro-

cessor to access the common memory. Such a time lasts on the average 1/µ

1

units of time, and ends when transition T

end1

fires returning the net to its

initial state. Obviously, a similar processing cycle is possible for processor

2 and many interleavings between the activities of the two processors may

Search WWH ::

Custom Search