Image Processing Reference

In-Depth Information

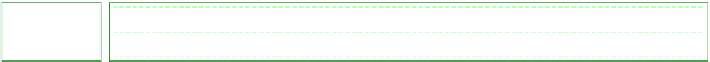

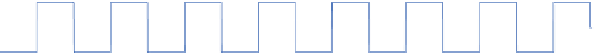

Simulation Results

max: 1.00e+000

i1

min: -1.00e+000

max: 1.00e+000

i2

min: -1.00e+000

max: 1.00e+000

i4

min: -1.00e+000

max: 1.00e+000

i3

min: -1.00e+000

max: 1.00e+000

i5

min: -1.00e+000

max: 9.55e-001

out

min: -9.54e-001

0

99

198

297

396

495

594

693

792

891

990 1089 1188 1287 1386 1485 1584 1683 1782 1881 1980 2079 2178 2277 2376 2475 2574 2673 2772 2871 2970

Fig. 4.10

Simulation of the QCA circuit for morphological erosion

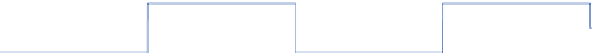

This operation can be designed on hardware by implementing a 5-input OR gate

as shown in Fig. 4.11, applying as inputs (i1 to i5) the values of the five input image

pixels that coincides to the five structuring element black pixels. In this figure the

“1” denotes the polarization of the fixed cell that corresponds to logic “1”.

The realization of the 5-input OR gate is made by the proper connection of four

2-input OR gates, which are realized by clamping one input of the 3-input majority

gate to logic “1”. In the design the maximum wire length in a clocking zone is kept

to 5 cells and the minimum distance between to wires is 2 cells.

The output of the 5-input OR gate will be logic “1” if one or more of the inputs

are set to logic “1”. So, if one or more of the pixels of the input image (which

coincides with the structuring element) are black, then the pixel of the origin on the

output image will be black. In other cases, the output will be logic “0”, so the output

pixel will be white.

According to QCADesigner tool the design consists of 35 cells covering an area

of 198

218 nm

2

m

2

. It is covering an orthogonal

×

that is approximately 0

.

043

µ

region of 10

11 grids and the ratio of the area covered by QCA cells to the overall

orthogonal region area of the layout is 0

×

318.

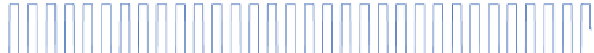

Fig. 4.12 presents the simulation results of the QCA morphological dilation op-

eration, which confirms the correctness of the design. As it is shown, all possible

value combinations of 5 inputs are applied to the circuit. The output is set to logic

“1” when one or more of the inputs stay at logic “1” otherwise is set to logic “0”

indicating the OR gate behaviour.

.

Search WWH ::

Custom Search