Image Processing Reference

In-Depth Information

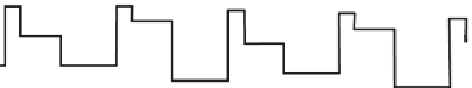

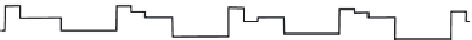

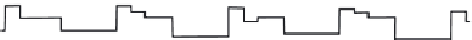

Schematic circuit diagrams of a combination of an FDA and CDS, and that of the opera-

tion with an applied clock pulse and potentials and CDS output are shown in Figure 3.10a

and b, respectively. Figure 3.10a shows a more practical circuit by introducing a low-pass

filter (LPF) to remove higher-frequency components to reduce aliasing, which become a

false signal and will be discussed in Section 6.1. An amplifier is also introduced between

node A and the sampling part for a higher accuracy of the sampled potential than that

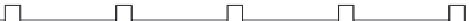

shown in Figure 2.26. In Figure 3.10b, ϕR, ϕCL, and ϕSH are the reset pulse, clamp pulse,

and sampling pulse, which are applied to the reset transistor, clamp transistor, and sam-

pling transistor, respectively.

The operation starts from the FD reset step, as shown in steps (4) and (1) in Figure 3.9, to

set the FD potential to the reset drain voltage

V

RD

. Then, the reset FD potential is detected

and output by the SFA in the FDA. After the reset FD potential signal is transmitted to node

A, node A is clamped to clamp voltage

V

cl

. Then, the signal charge packet is transferred

to the FD as shown in step (2) in Figure 3.9. The potential of the FD changes to the level at

which FD contains signal charges, as shown in step (3) in Figure 3.9b, and is detected and

output by the SFA as well. Since the FD potential, which is the input of SFA, changes, the

output of SFA and necessarily the input to CDS follow. The SFA output amount of change

caused by signal charges is transmitted to node A through the AC coupling capacitor

C

c

.

Then, the potential at node A is amplified and sampled at sampling capacitor

C

sh

by the

sampling transistor. This is one cycle of CDS operation. Thus, the potential at node A

corresponding to the reset level is forced to be clamped to

V

cl

by a clamp pulse after each

reset operation, as shown at node A in Figure 3.10b. And the CDS circuit accepts only the

change by signal charge packet transfer into the FD. Reset noise causes changes in FD

potential by the reset operation, as shown in Figures 3.9b and 3.10a. But any reset noise can

be removed by CDS in this way. Outside of reset noise, 1/f noise discussed in Section 3.3.1

occurs at the drive transistor in SFA, as shown by the dashed line at the FDA output in

Figure 3.10b. Since its power spectrum is high in the lower-frequency area, the change in

the time domain is very slow, as shown in the figure. Therefore, the level of 1/f noise at

the time of the clamping and sampling operation can be considered almost equal, because

(a)

V

RD

V

dd

Node A

1/f noise

φR

φ

SH

C

c

Signal charge

LPF

CDS

output

FD

FDA

output

φCL

V

cl

C

sh

Reset noise

FDA

CDS

(b)

Feedthrough period

Signal period

Reset noise

Fluctuation by 1/f noise

FDA output

True

signal

level

φ R

φ CL

φ SH

Node A

V

cl

O

CDS

output

FIGURE 3.10

CDS: (a) circuit configuration of FDA and CDS combination; (b) schematic diagram of CDS operation.