Image Processing Reference

In-Depth Information

V

d

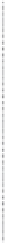

Reset transistor

CDS

SFA

Q

FD

FDA

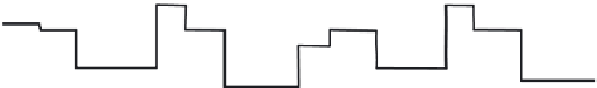

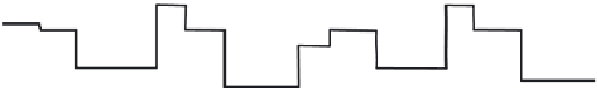

FIGURE 2.26

Block diagram of FDA and CDS circuit connection.

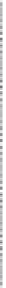

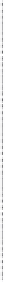

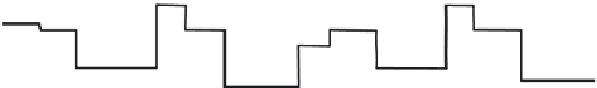

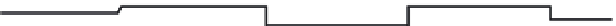

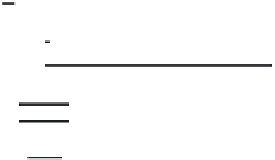

The principle construction of a CDS circuit

4

is shown in Figure 2.27a. The input follows

the SFA output in an FDA and an alternating current (AC) coupling capacitor

C

c

transfers

only the AC component to node A. A clamp transistor that connects node A and the clamp

voltage

V

clamp

source is formed, and clamp pulse ϕ

CL

is applied to the gate electrode. A sam-

pling transistor to which sampling pulse ϕ

SH

is applied at the gate electrode and capacitor

C

SH

is formed to sample and hold the potential of node A.

φ

SH

Sampling

transistor

C

c

Node A

Output

Input

Clamp

transistor

C

SH

φ

CL

V

clamp

(a)

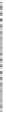

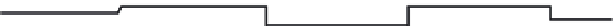

Reset level

Reset level

Reset level

Reset level

Input

Signal

component

Signal level

Correlated

Correlated

Signal level

Correlated

Signal level

Signal level

Correlated

φ

CL

φ

SH

Node A

V

clamp

Signal

component

Signal

component

Signal

component

Signal

component

V

clamp

Output

Signal

component

Signal

component

Signal

component

Signal

component

(b)

FIGURE 2.27

CDS circuit: (a) configuration; (b) principle operation.