Image Processing Reference

In-Depth Information

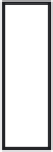

(e)

V

G

> 0 V

p

Shallow depletion layer

(f )

Conduction band

Shallow depletion layer

p

- 0 V

V

G

> 0 V

Valence band

FIGURE 2.10

(Continued)

First, when negative voltage is applied to the gate electrode, the holes gather in the sili-

con surface because of their positive charge, as Figure 2.10c shows by spatial distribution.

As shown by energy distribution in Figure 2.10d, the holes in the

p

-type semiconductor are

attracted to the lower energy state formed by the negative potential of the gate electrode

and accumulated in the silicon surface. This hole layer is called the surface accumulation

layer. The electron layer accumulated in the silicon surface by the application of a posi-

tive voltage to the gate electrode in the

n

-type silicon MOS state is also called the surface

accumulation layer.

Next, as Figure 2.10e shows by spatial distribution, the application of a low positive volt-

age, less than about 1 V, to the gate electrode causes holes to take off from the surface

and only the negatively charged ionized acceptors remain, forming a depletion layer. In

Figure 2.10f, this is shown as an energy distribution: holes escape from the higher poten-

tial surface area caused by the positive potential of the gate electrode.

The higher positive voltage application to the gate electrode indicated in Figure 2.10g

shows that the depletion layer extends deeper inside the semiconductor and the width

(depth) enlarges as spatial distribution, as also shown in energy space in Figure 2.10h.

The rough indication of deep depletion is thought to be a gate voltage higher than about

1.1 V, which corresponds to the silicon bandgap at room temperature. In this situation, if