Image Processing Reference

In-Depth Information

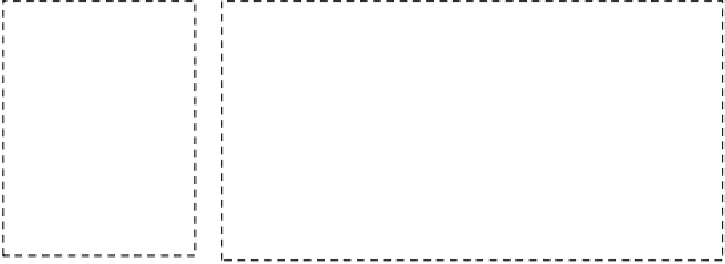

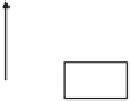

V

DD

= 2.8 V

V

DD

= 1.2 V

V

pix

Pixel

Delta-sigma modulator

φ

RST

φ

R1

φ

R1

φ

T1

a

Z

-1/2

b

Z

-1/2

+

+

1-

Z

-1

1-Z

-1

-

-

φ

T2

φ

S

Pixel out

φ

R1

φ

R1

Z

-1/2

Z

-1/2

D

M

=1b

φ

R2

φ

BW1

1

Q

D

φ

R1

0

Q

CK

+

F

0

14 bits

+

Decimation filter with CDS

Data bus

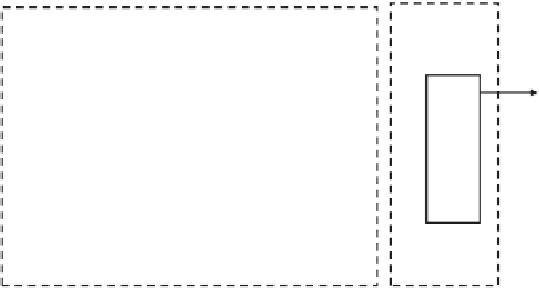

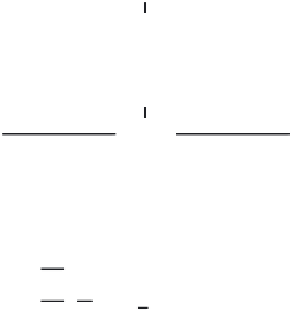

FIGURE 5.63

Schematic diagram of the column readout circuit. (Reprinted with permission from Chae, Y., Cheon, J., Lim, S.,

Lee, D., Kwon, M., Yoo, K., Jung, W., Lee, D., Ham, S., and Han, G.,

Proceedings of the IEEE International Solid-State

Circuits Conference, Digest of Technical Papers

, 22.1, pp. 394-395, San Francisco, CA, 2010.)

The reasons second-order ΔΣ ADCs are adopted rather than first-order ones are as

follows:

1. Conversion 2

N

times is necessary to obtain

N

bits in the case of a first-order ΔΣ

ADC, and a high-speed clock over 1 GHz is necessary to obtain 12 bits.

2. Since pixel signal to be converted is DC signal, the number of times of conversion

is limited and it is not converted accurately by a first-order ΔΣ ADC.

3. In the case of first-order ΔΣ ADCs, high amplification gain of about 70 dB is

required to avoid band of frequency loss at conversion.

Thus, it is considered that this sensor needs to elaborate the well-balanced design in

the 2.25 μm pixel pitch with dual-channel output by adopting a second-order ΔΣ ADC to

achieve high performance, such as 12-bit resolution at a high frame rate of 120 fps, 13-bit

resolution at 60 fps, low-noise performance, low power consumption, and a high dynamic

range of the ADC.

As described above, column-parallel ADC sensors have been realized by various types

of ADC, and some have become a commercial reality. Depending on the development of

CMOS process technology such as downscaling and circuit design technology, the bound-

ary conditions for the best technical choice might change. This should be aimed for in any

future development.