Image Processing Reference

In-Depth Information

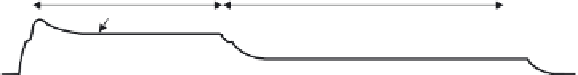

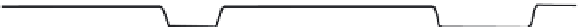

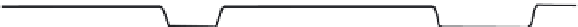

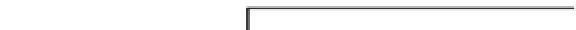

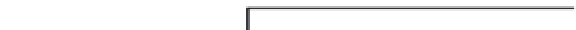

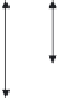

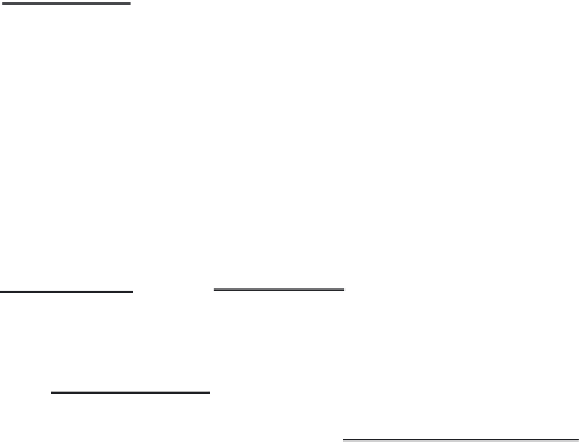

Reset signal conversion

Sensor signal conversion

Reset signal

Sensor signal

Pixel output

Ramp wave

(D/A output)

Agreement of ramp wave

and pixel output

Comparator

output

Up/down switching

Up/down

setting signal

PLL clock

Digital CDS

output

Down count start

Up count start

Counter

output

Reset signal

count

Sensor signal

count

Down counting

Up counting

FIGURE 5.57

Timing chart of digital CDS by single-slope integration. (Reprinted with permission from Nitta, Y., Muramatsu, Y.,

Amano, K., Toyama, T., Yamamoto, J., Mishina, K., Suzuki, A., et al.,

Proceedings of the IEEE International Solid-

State Circuits Conference, Digest of Technical Papers

, 27.5, pp. 2024-2031, San Francisco, CA, 2006.)

counter digitally subtracts conversion of the reset signal from the sensor signal, as shown

by counter output in Figure 5.57. In this way, the difference between the sensor and reset

signals is obtained in the digital domain, so it is called digital CDS. The obtained digital

data are transferred to data latches in each counter block. The horizontal data transfer and

A/D conversion of the next row are processed in parallel.

This configuration has the advantage of low-noise performance because of not only

highly accurate offset noise cancelation but also a lower band of frequency, thanks to A/D

conversion by column-parallel processing. By column-parallel A/D conversion, the sen-

sor achieves a high frame rate of 180 fps

44

in spite of the larger pixel number of 2.8 M. The

digital resolution is 12 bits. The noise of the electron number of column FPN by digital

CDS is reported to be 0.5.

As circuits of single-slope integrating type ADC are rather simple, they can be used

for narrow-pitch pixel sensors. They are suitable for image sensors because of their lower

power consumption. On the other hand, a significantly shorter conversion time is neces-

sary to increase the number of bits for digital coding. It is not easy to achieve both high

speed and high digital resolution.

5.3.3.2.2.2 Successive-Approximation-Type ADC

Successive-approximation ADC (SA-ADC)

is used as column ADC to realize high-speed conversion. Digital codes of all bits are

counted, starting from the most significant bit and finishing at the least significant bit. DAC