Image Processing Reference

In-Depth Information

Pixel

Pixel

Pixel

Chip

ADC

Pixel

ADC

Column

ADC

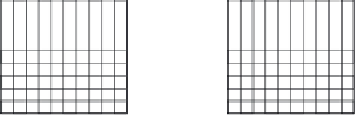

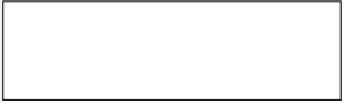

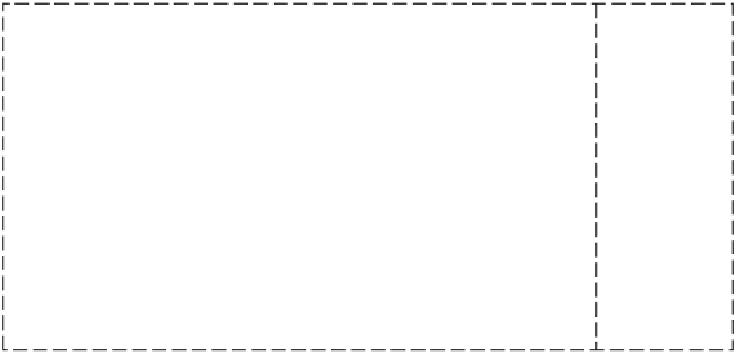

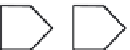

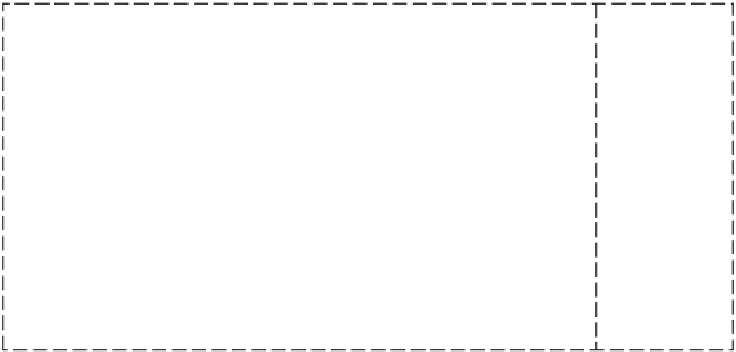

(a)

(b)

(c)

FIGURE 5.53

Stages of signal digitization: (a) chip-level ADC; (b) column-level ADC; (c) pixel-level ADC.

Figure 5.53b. Since A/D conversion is parallelized in lower bandwidths, <1 MHz,

it has an advantage in noise performance. Digitized signal can be output at speeds

10 times higher than in chip-level ADC sensors.

3. Pixel-level ADC sensor. Stretching much further back to the source, an ADC is

formed at each pixel in this configuration, as shown in Figure 5.53c. Because of

pixel-parallel processing, A/D conversion in even lower bandwidths is possible.

Currently these sensors are still being researched

42

and are for special use only,

because many transistors are necessary at each pixel, among other reasons.

5.3.3.2.1 Chip-Level ADC Sensor

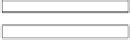

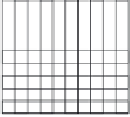

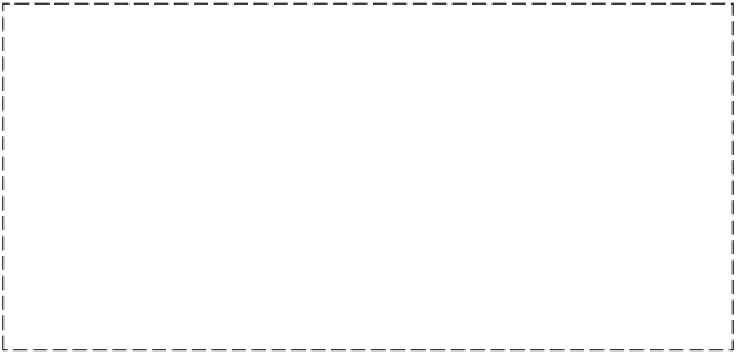

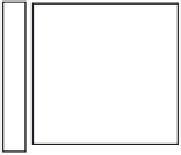

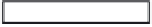

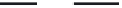

An example of a chip-level ADC sensor is shown in Figure 5.54.

43

Since an analog signal

with pixel output frequency around 30 MHz is digitized, the same range of bandwidth

of ADC is necessary. Green pixel signals and red/blue pixel signals are read out from the

top and bottom channels, respectively, making this sensor dual channel. Each channel

has a pipeline ADC, which is suitable for high-speed conversion by parallel processing

serial signals. Since circuit size increases in proportion to step number, pipeline ADCs are

Column decoder

Green

column S/H

Top-channel readout: green

PGA1

PGA2

12-bit pipeline ADC

Pixel array

3264(H) × 2448(V)

Bottom-channel readout: red/blue

Red/blue

column S/H

PGA1

PGA2

12-bit pipeline ADC

Column decoder

FIGURE 5.54

Block diagram of a chip-level ADC sensor. (Reprinted with permission from Cho, K., Lee, C., Eikedal, S.,

Baum, A., Jiang, J., Xul, C., Fan, X., and Kauffman, R.,

Proceedings of the IEEE International Solid-State Circuits

Conference, Digest of Technical Papers

, 28.5, pp. 508-509, 2007.)