Information Technology Reference

In-Depth Information

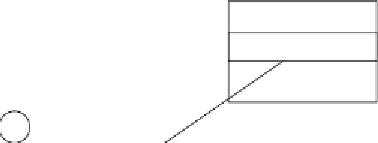

Pour accélérer les accès à la mémoire centrale et compenser le coût lié à la pagi-

nation, un cache associatif (

TLB look-aside buffers

) est placé en amont de la mémoire

centrale. Ce cache associatif contient les couples

<

numéro de page p, adresse d'implan-

tation de la case contenant p

les plus récemment accédés. Lorsque la MMU doit

effectuer une conversion d'adresse paginée, elle cherche tout d'abord dans le cache

si la correspondance

>

>

n'est pas dans le cache. Si non, elle accède à la table des pages en mémoire centrale

et place le nouveau couple référencé dans le cache. Si oui, elle effectue directement

la conversion : un seul accès mémoire est alors nécessaire pour accéder à l'octet

recherché (figure 13.12).

La taille des pages est souvent choisie comme étant un compromis entre la taille

de la table des pages et la fragmentation interne possible. Ainsi, opter pour une petite

taille de pages (inférieure à 4 Ko) diminue le problème de fragmentation interne,

mais conduit à une plus grande table des pages pour chaque processus. Au contraire,

augmenter la taille des pages augmente le risque de fragmentation interne, mais

amène à de plus petites tables des pages.

<

numéro de page p, adresse d'implantation de la case contenant p

Cache associatif

MMU

p, c

adr

Adresse logique

Registre PTBR

Table des pages

pd

adr

c

p

1

non

trouvé

trouvé

+

2'

+

3'

c

2

+

Page

d

Adresse

physique

Mémoire

Figure 13.12

Traduction d'une adresse paginée

en adresse physique avec ajout d'un cache associatif.

➤

Protection de l'espace d'adressage des processus

Des bits de protection sont associés à chaque page de l'espace d'adressage du processus

et permettent ainsi de définir le type d'accès autorisés à la page. Ces bits de protec-

tion sont mémorisés pour chaque page, dans la table des pages du processus. Classi-

Search WWH ::

Custom Search