Information Technology Reference

In-Depth Information

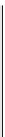

Processeur

Cache de niveau 1

Cache de niveau 2

Mémoire centrale

SRAM

Bus local

Instructions

MMU

DRAM

Données

Bus

Adresse virtuelle Adresse physique

Figure 8.22

Implantation du module MMU dans le processeur.

donc ralentit le processus d'exécution. Il est préférable de placer ce type de table

dans le cache afin d'accéder à son contenu le plus rapidement possible.

Le mécanisme de gestion de mémoire virtuelle n'est pas conceptuellement diffé-

rent du mécanisme de gestion des caches. La différence porte essentiellement sur

l'implantation de ces mécanismes. Par exemple dans le cas des caches les algorithmes

de remplacement sont pris en charge par le matériel (algorithme hardware) alors que

pour la mémoire virtuelle cette gestion est logicielle (prise en compte par le système

d'exploitation).

Il y a plusieurs mécanismes possibles pour la gestion de la mémoire virtuelle,

taille des blocs fixe ou variable, implication des programmeurs ou transparence au

niveau de la programmation, implication de modules matériels ou non. Ces ques-

tions d'implantation du mécanisme de gestion de la mémoire virtuelle sont détaillées

dans le chapitre relatif aux systèmes d'exploitation traitant de la gestion de la mémoire.

8.5

COMPLÉMENTS : APPROCHES CISC/RISC

L'objectif de ce complément sur les approches CISC et RISC est d'éclairer les diffé-

rences les plus marquantes concernant ces deux types de processeurs et de montrer

les architectures matérielles qu'ils engendrent. Il ne s'agit pas de faire une compa-

raison exhaustive, encore moins des mesures comparatives, de ces deux classes de

processeurs mais plutôt de dégager les raisons principales expliquant cette évolution

du CISC au RISC.

Dans une première période les évolutions technologiques ont permis aux architectes

d'augmenter les fonctionnalités et les performances des processeurs et des ordina-

teurs. Ces évolutions ont conduit à une architecture typique comportant un petit nombre

Search WWH ::

Custom Search