Information Technology Reference

In-Depth Information

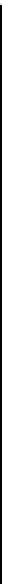

1 signifie que le signal d'horloge est présent, dans le cas

contraire le signal est égal à 0.

Ainsi le circuit déclencheur a une sortie à 1 à chaque top horloge si le signal

AttenteMémoire est faux ou si le signal AttenteMémoire est vrai et que la mémoire

est prête.

Le générateur d'étapes est un compteur d'étapes qui admet comme signal d'entrée

le signal de sortie du déclencheur. Il incrémente le numéro de l'étape à chaque fois

que la sortie du déclencheur est à 1.

La notation « horloge »

=

D

é

c

l

e

n

c

h

e

u

r

Générateur d'étapes

Horloge

1 2 3 4 5 6 7 8

Signal Mém

oire Prête

Circuits ET

Registre

Instruction

RI

Yen

InCo

Ret

Zen

Zsor

Ren

Rsor

Lect

Add

COen

COsor

RIen

RIsor

RADen

RDOsor

Load D, R, B

Circuits OU

AttenteMemoire

Figure 7.20

Séquenceur câblé.

La figure 7.20 montre la complexité du « câblage » d'un tel séquenceur et illustre

la terminologie « séquenceur câblé ». Ces séquenceurs très complexes dans leur

réalisation sont très performants car entièrement constitués de circuits électroniques.

Par contre aucune erreur n'est permise lors de leur réalisation car il est impossible de

modifier le câblage. Enfin il est impossible d'ajouter une instruction qui pourrait être

utile après la réalisation d'un tel circuit.

Search WWH ::

Custom Search