Information Technology Reference

In-Depth Information

➤

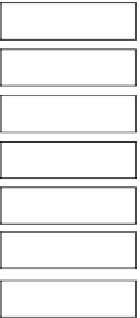

Étape 3

Cette étape se produit 30 nanosecondes après la demande de lecture faite par le

microprocesseur. Elle consiste à placer le contenu du registre RDO dans le registre

instruction RI. À la fin de cette étape le registre d'instruction RI contient l'instruc-

tion Add D, R, A. La phase de recherche et de chargement (FETCH) de l'instruction

dans le registre d'instruction RI est alors terminée. La phase de décodage commence

(figure 7.8).

Y

Z

10

Load D, R, B

PSW

11

Add D, R, A

12

Store D, R, C

R

3

13

Horloge

A

14

5

CO

12

B

15

3

Décodeur

16

Add D, R, A

RDO

C

17

Add D, R, A

RAD

Add D, R, A

0 1 2 30 31 61 62 63

Tops horloge microprocesseur

Figure 7.8

Étape 3.

Décodage

La phase de décodage permet l'interprétation du code opération et du mode d'adres-

sage de l'opérande. Ici il s'agit d'une addition du contenu de l'adresse mémoire A

avec le registre R, le résultat devant être placé dans R. Cette phase va permettre

d'acquérir le contenu de A qui sera placé dans le registre Y. La phase d'exécution

pourra alors être réalisée.

Search WWH ::

Custom Search