Information Technology Reference

In-Depth Information

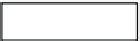

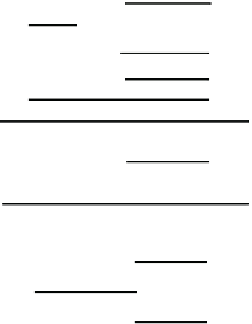

Y

Z

10

Load D, R, B

PSW

11

Add D, R, A

12

Store D, R, C

R

3

13

Horloge

A

14

5

CO

11

Séquenceu

r

B

15

3

16

Décodeur

RI

C

17

RDO

RAD

0 1 2 30 31 61 62 63

Tops horloge microprocesseur

Figure 7.5

Machine et programme de l'exemple.

L'ensemble des registres est (pour des raisons de simplicité graphique) réduit à un

seul registre (R).

Notre machine a les caractéristiques suivantes :

- la fréquence du processeur est égale à 1 GHz, soit un cycle égal à 1 ns;

- la fréquence du bus est égale à 66 MHz, soit un cycle égal à 15 ns ;

- le temps d'accès à la mémoire centrale est égal à 20 ns.

Le bus de communication est de type synchrone. Ainsi lorsque le microprocesseur

fait une demande de lecture mémoire il obtiendra sa donnée 30 nanosecondes plus

tard (après deux cycles du bus).

Les instructions de notre machine sont de type registre/mémoire : l'un des opérandes

est en mémoire, l'autre est dans un registre. Avec ce type d'instructions notre problème,

C

=

B s'exprime sous la forme de la séquence d'instructions :

load D, R, @B

A

+

Charger le contenu du mot d'adresse B

➥

dans le registre R. (R) = (B)

add D, R, @A

(R) = (R) + (A)

Contenu de R + contenu de A dans R

store D, R, @C

(C) = (R)

Placer le contenu de R à l'adresse C

Search WWH ::

Custom Search