Information Technology Reference

In-Depth Information

7.2.2

Les bus

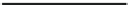

Comme le schéma général de la figure 7.3 le montre notre ordinateur est d'une part

organisé autour d'un bus interne au microprocesseur, d'autre part autour d'un bus

externe au microprocesseur servant pour la communication entre la mémoire et le

microprocesseur. Le bus interne est unique dans notre cas.

Y1

Opération

Z

Unité Arithmétique

et Logique

Y2

Bus interne

Données

Registres

Commandes

Séquenceur

Décodeur

Unité de Commande

RI

CO

RAD

RDO

Commandes Lecture/Écriture

Adresses

Données

Bus Processeur / Mémoire

Figure 7.3

Schéma général du processeur.

La conception et l'organisation du microprocesseur, en particulier du, ou des bus

internes, laisse une grande liberté au concepteur. Par contre le bus externe est beaucoup

plus contraint du fait de la grande variété des modules matériels à interconnecter.

Ce type de bus s'appuie sur des caractéristiques importantes telles que : la largeur

du bus, le cadencement du bus, l'arbitrage pour l'accès au bus, les modes de fonction-

nement du bus.

Dans cette section nous étudions les modalités d'exécution des instructions machine.

Ces modalités concernent le fonctionnement et l'organisation du bus interne et les

aspects largeur et cadencement du bus externe. Les aspects arbitrage et modes de

fonctionnement seront abordés respectivement, dans le chapitre 9 traitant des entrées-

sorties et dans le chapitre 8 traitant de la gestion des caches mémoire.

Largeur du bus

La

largeur

du bus définit le nombre de lignes du bus c'est-à-dire le nombre de bits

que le bus peut véhiculer en parallèle. Cette largeur de bus constitue une donnée

technique très importante et plus particulièrement la largeur du bus d'adresses. En

effet, plus le bus d'adresses est large plus l'espace d'adressage du processeur est

Search WWH ::

Custom Search