Information Technology Reference

In-Depth Information

Clock

1

Clock

2

Clock

1

M

P1

M

P2

2 3

Clock

2

V

1

V

IN

V

OUT

C

1

V

1

1

4

C

2

1 4

V

OUT

M

N1

M

N2

2 3

Clock

1_n

Clock

2_n

time

(a)

(b)

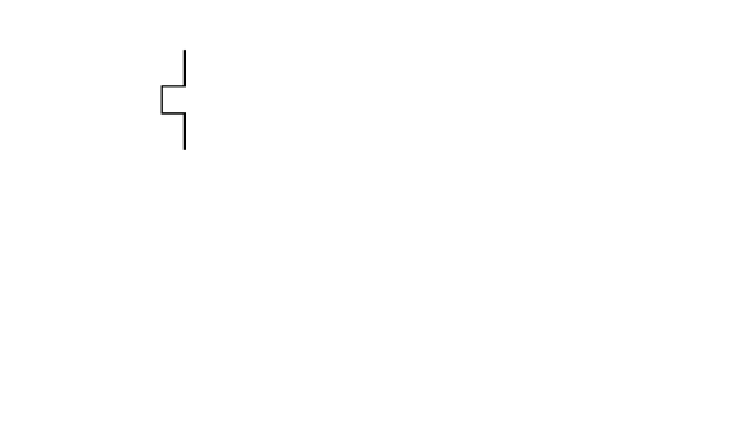

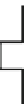

Fig. 2. (a) Schematic of a simple circuit consisting of two inverters connected in series,

utilizing 2-level Bennett clock. The blue arrows indicate the current flow during the

computation (1 and 2) and de-computation (3 and 4). (b) Timing diagram of the Bennett clocks

and

the

voltages

V

1

and

V

OUT

,

transitions

during

the

computation

(1

and

2)

and

the

de-computation (3 and 4) (Color figure online).

3.

De-compute V

OUT

: The second level clocks starts to ramp back to 0 V while the

first level clocks are still held constant. Capacitor C

2

gradually gets discharged

through M

P2

, and the voltage level at V

OUT

gradually drops back to 0 V.

4.

De-compute V

1

: When the second level clocks are relaxed, the first level clocks

start to relax back to 0 V. Capacitor C

1

is gradually charged, and the voltage level

at V

1

gradually rises back to 0 V. After this, the input V

IN

is relaxed.

3

Arithmetic-Logic Unit Design

A Bennett-clocked arithmetic logic unit (ALU) was designed based on the commer-

cially available SN74S381N [

20

], which can perform three arithmetic and three logic

operations on two active high unsigned 4-bit words A = (A

3

,A

2

,A

1

,A

0

) and

B = (B

3

,B

2

,B

1

,B

0

), producing the 5-bit result word F = (F

4

,F

3

,F

2

,F

1

,F

0

). Neg-

ative result numbers are represented in the two's complement format. The function

mode is set with three additional active high select signals S

2

-S

0

, to implement an

operation from the set {clear/reset, B minus A, A minus B, A plus B, A xor B, A or B,

A and B, preset} according to Table

1

. The implemented structure is capable of

operating either in irreversible standard CMOS mode or the reversible Bennett

clocked mode.

3.1

Logical Structure and Implementation

The logic schematic of the ALU using standard gate set {not, nand, nor, xor} is shown

in Fig.

3

, having the longest combinatorial path of 11 logic levels in the final

implementation. In this schematic, no clocks are shown, and only the data signals

Search WWH ::

Custom Search