Information Technology Reference

In-Depth Information

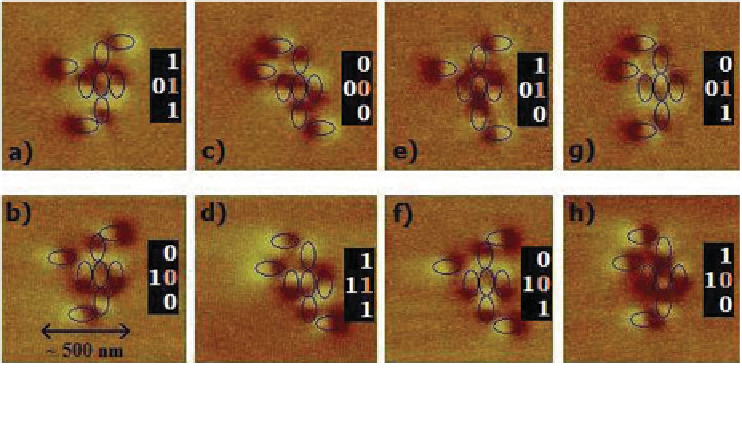

Fig. 4. Experimental demonstration of an NML three-input majority-logic gate. (Source: Imre

et al., Ref. [

13

].)

Thus far [

16

-

18

], our work has provided a proof-of-concept demonstration of

NML - i.e. the feasibility of performing digital logic with physically-coupled nano-

magnets. However, so far we have used MFM to read the state of the dots, and

externally generated magnetic fields to switch the dots. Of course, this is not practical

for real applications. Below, we describe on-going work to develop electronic input

and output (I/O) and mechanisms for generating local magnetic fields for ''on-chip''

clocking.

Before proceeding, we want to emphasize that our experimental proof-of-concept

demonstrations satisfy five ''tenets'' that are considered essential for a digital system:

(1) NML devices have non-linear response characteristics due to the magnetic hys-

teresis loop. (2) NML can deliver a functionally complete logic set enabled by the

3-input majority gate and the NOT operation naturally achieved by the antiferro-

magnetic dot-to-dot coupling. (3) Signal amplification/gain greater than 1 has been

experimentally demonstrated by showing the feasibility of 1:3 fanout [

19

], where the

energy for the gain is provided by an external clocking field discussed further below.

(4) The output of one device can drive another as the fringing fields from individual

magnets can bias a neighbor. (5) Unwanted feedback is preventable through clocking.

4

Nanomagnet Logic: Towards System Integration

Recent and ongoing work addresses electronic means for both NML I/O and clocking.

Our approach leverages existing MRAM technologies for READ/WRITE operations.

After all, setting an input for NML, i.e. setting the state of an input magnet, is similar

to writing the state of an MRAM bit. Similarly, reading the state of an NML output dot

is just like reading an MRAM bit. These similarities to MRAM suggest that an NML

circuit is analogous to a patterned ensemble of the free layers in an MRAM stack.

Search WWH ::

Custom Search