Information Technology Reference

In-Depth Information

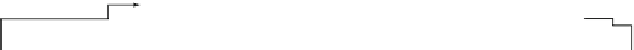

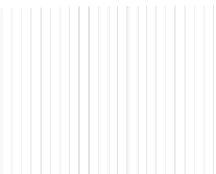

MULTIPLIER

ADDER

LOOP = 52 Clock Cycles

LOOP

A)

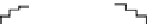

LOOP

LOOP

LOOP = 10 Clock Cycles

LOOP

LOOP

B)

ADDER

MULTIPLIER

Fig. 16.

Redesign of MAC to reduce the loop length. With this new design the loop

length is only 10 clock cycles, moreover it is independent from the bit number.

major sources of performance degradation in this technology, the shorter the

loop, the better the performance. With a better analysis of the circuit layout,

the MAC circuit can be modified as shown in Fig.

16

, so the original 52 clock

cycle long loop has become only 10 clock cycle long, without changing the sys-

tem algorithm. The delay is also independent from the MAC bit number, and

overall the area is smaller. Without interleaving the delay between one data and

the next is therefore of only 10 clock cycles.

Figure

17

shows a simulation comparison (without interleaving) of the origi-

nal architecture (Fig.

17

(A)) and the optimized one (Fig.

17

(B)). The execution

time, and therefore the throughput, is improved of 5 times. While this technique

shows good results, it can be only used as a complementary technique, because

it does not allow to completely eliminate the loop. Interleaving is still necessary,

however the number of operations required to reach maximum performance is

lower.

3.2 Signals Synchronization

While the loss of performance is probably the more relevant problem due to

the presence of loops, some important issues also arise for signals synchroniza-

tion. When more loops are present inside the circuit, they must be carefully

designed to achieve perfect signals synchronization. Another issue is related to

the necessity of adding a specific delay on a particular signal. This is a common

requirement in many circuits, where the algorithm mapping implies the necessity

of delaying some signals of a specific amount of clock cycles. In case of NML and

all the intrinsic pipelined technologies particular rules must be followed to add

delays on specific signals. Both problems and the related solutions are described

in the following.

Search WWH ::

Custom Search