Information Technology Reference

In-Depth Information

WL

1

WL

2

WL

4

WL

3

Horz. Inter.

X

21

X

22

X

23

r

1

−−

−−

−

X

1

S

a

S

b

r

2

Horz. Inter.

X

5

X

6

X

7

X

18

F

1

Vert. Inter.

OR

r

3

A

X

2

X

11

−

X

17

r

4

X

13

X

14

X

15

X

16

S

−

F

3

Horz. Inter.

D

ifferential Output

Generator

r

5

X

3

X

12

X

19

B

S

Vert. Inter.

r

6

X

8

X

9

X

10

X

20

F

2

Horz. Inter.

Bit Line

X

24

X

25

X

26

r

7

A

−

X

4

S

a

S

b

Source Line

Horz. Inter.

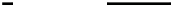

Fig. 6.

Layout of 2-input exclusive-OR.

by fixing one of the inputs to 0/1. In Fig.

6

,(

X

1

,

X

2

,

X

5

,

F

1

) forms a

2-input AND gate with inputs

X

1

(=

x

1

)and

X

2

(=

x

ₓ

2

) and output

X

5

(=

x

1

· x

ₓ

2

).

F

1

is the fixed cell. Similarly, (

X

3

,

X

4

,

X

6

,

F

2

) forms a second

2-input AND gate with inputs

X

3

(=

x

ₓ

1

)and

X

4

(=

x

2

) and output

X

6

(=

x

ₓ

1

· x

2

). (

X

11

,

X

12

,

X

13

,

F

3

) forms a 2-input OR gate.

X

11

(=

x

1

· x

ₓ

2

)

and

X

12

(=

x

ₓ

1

· x

2

) are the inputs and

X

13

(=

x

1

· x

ₓ

2

x

ₓ

1

· x

2

)isthe

+

output.

F

3

is the fixed cell.

(b)

Interconnects:

These are the cells that propagate information across the

logic, just like wires in CMOS circuits. However unlike CMOS, the infor-

mation here flows without the flow of any physical entity. These intercon-

nects are of two types: vertical and horizontal. In a vertical interconnect,

the information flows with the help of ferromagnetic coupling. In Fig.

6

,

(

X

18

,

X

21

), (

X

20

,

X

24

) are two vertical interconnects. In a horizontal

interconnect, the information flows with the help of antiferromagnetic

coupling between the MTJs. In Fig.

6

,(

X

6

,

X

7

), (

X

9

,

X

10

), (

X

14

,

X

15

,

X

16

), (

X

21

,

X

22

,

X

23

), (

X

24

,

X

25

,

X

26

) are different horizontal intercon-

nects. Note that cells like

X

21

and

X

24

are at the intersection of both

types of interconnects.

(c)

Differential output generator:

They generate opposite output states with

the help of antiferromagnetic coupling. In Sect.

4.3

we will see how these

opposite states are used by the read circuit to read the output from

the logic. In Fig.

6

,(

X

15

,

X

16

,

X

17

,

X

19

) forms the differential output

generator.

3.

Output cells:

These are MTJs with access transistors that store the final

output and its complement. Again these cells are only clocked and are never

Search WWH ::

Custom Search