Information Technology Reference

In-Depth Information

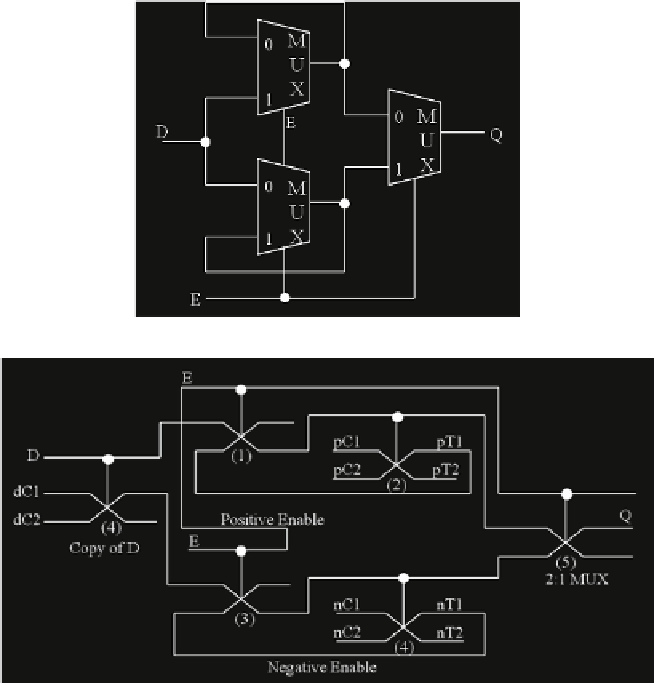

period thus frequency of the clock can be reduced to half of the master-slave

flip flop while maintaining the same data rate. The half frequency operations

make the DET flip flops very beneficial for low power computing as frequency

is proportional to power consumption in a circuit. The DET flip-flop is designed

by connecting the two latches, viz., the positive enable and the negative enable

in parallel rather than in series. The conventional design of the DET flip-flop

is illustrated in Fig.

13

(a) [

49

]. The 2:1 MUX at the output transfer the output

from one of these latches which is in the storage state (holding its previous state).

The equivalent testable reversible design of the DET flip flop is proposed in this

work and is shown in Fig.

13

(b).

In the proposed design of testable reversible DET flip-flop, the positive enable

testable reversible D latch and the negative enable testable reversible D latch

are arranged in parallel. The Fredkin gates labeled as 1 and 2 form the positive

(a) Conventional DET flip-flop

(b) Fredkin gate based DET flip-flop

Fig. 13.

Fredkin gate based double edge triggered (DET) flip-flop

Search WWH ::

Custom Search