Information Technology Reference

In-Depth Information

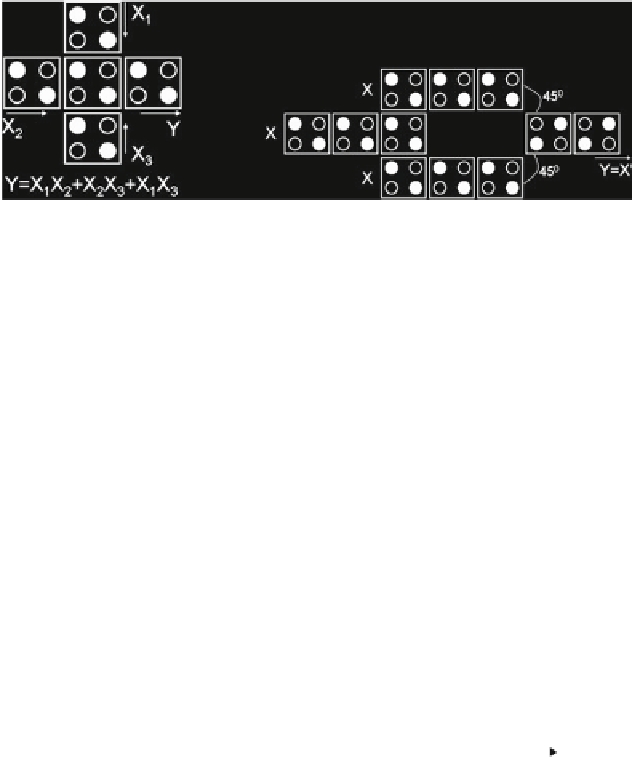

(a) Majority voter

(b) Inverter

Fig. 3.

QCA majority voter (MV) and inverter devices

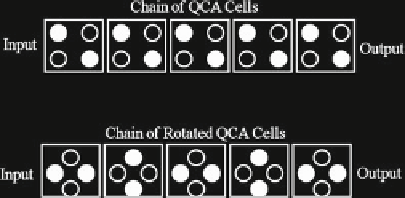

(a) Binary wire

(b) Inverter chain

Fig. 4.

QCA binary wire and inverter chain

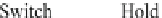

Fig. 5.

QCA 4 phase clocking

interesting contributions are made towards deriving exact minimal elementary

quantum gate realization of reversible combinational circuits. Any nanotechnol-

ogy having applications of reversible logic such as nano-CMOS devices, NMR

based quantum computing, or low power molecular QCA computing, all are sus-

ceptible to high device error rates. This attracted the attention of researchers

towards testing of reversible logic circuits. In [

48

], it has been shown that for

reversible logic circuits, the test set that detects all single stuck-at faults can also

detect multiple stuck-at faults. In [

50

], four fault models for reversible circuits,

viz., single missing gate fault, the repeated-gate fault, the multiple missing gate

fault and the partial missing-gate fault are proposed based on ion-trap quantum

Search WWH ::

Custom Search