Information Technology Reference

In-Depth Information

L

0

...

f

mux

f

mux

L

1

L

2

0

0

shift

shift

shift

...

...

...

...

f

add

f

and

f

not

...

...

...

MDR

INR

...

AC

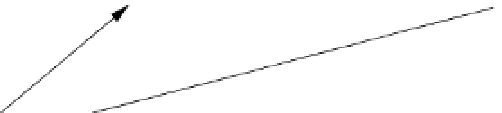

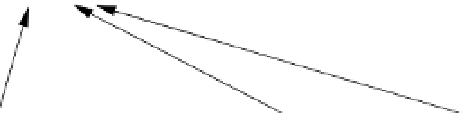

Figure 3.39

Circuits providing input to the accumulator AC.

The circuit for the program counter PC can be designed from an adder, a multiplexer, and

a few additional gates. Its size is proportional to

. The circuits to supply inputs to

the remaining registers, namely MAR, MDR, OPC, INR, and OUTR, are less complex to

design than those for the accumulator. The same observations apply to the control variable to

write the contents of the memory. The complete design of the CPU is given as an exercise (see

Problem

3.41

).

log

2

m

3.10.6 CPU Circuit Size and Depth

Using the design given above for a simple CPU as a basis, we derive upper bounds on the size

and depth of the next-state and output functions of the RAM CPU defined in Section

3.4

.

All words on which the CPU operates contain

b

bits except for addresses, which contain

bits where

m

is the number of words in the random-access memory. We assume that

the CPU not only has an

log

m

-bit program counter but can send the contents of the PC

to the MAR of the random-access memory in one unit of time. When the CPU fetches an

instruction that refers to an address, it may have to retrieve multiple

b

-bit words to create an

log

m

-bit address. We assume the time for such operations is counted in the number

T

of

steps that the RAM takes for the computation.

The arithmetic operations supported by the RAM CPU include addition and subtraction,

operations realized by circuits with size and depth linear and logarithmic respectively in

b

,the

log

m

Search WWH ::

Custom Search