Information Technology Reference

In-Depth Information

4 Experimental Analysis

This section reports the experimental analysis of the proposed MultiBSP bench-

mark. First, we introduce the problem instances by describing the main features

of the architectures used to test the benchmark. After that, the numerical results

and the values for the

g

and

L

parameters are reported. Finally, the validation

of our results using a real MultiBSP program is presented.

4.1 MultiBSP Architectures Used in the Experimental Analysis

For our experiments, the hierarchical levels of the considered architectures are

specially relevant. The main goals of the experimental analysis are to verify

the proper functionality of the proposed benchmark and also to compute the

corresponding values for the parameters of the MultiBSP model.

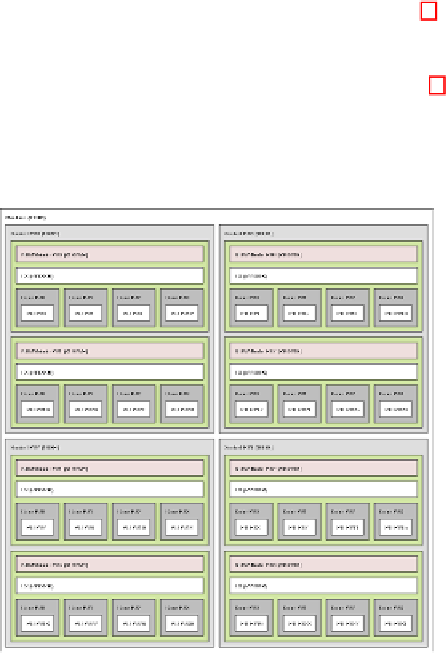

We selected two real infrastructures for the experimental analysis, which fea-

ture a reasonably large number of cores and interesting cache levels:

-

Instance #1 is

dell32

, whose architecture is shown in Fig. 5.

dell32

has four

AMD Opteron 6128

Magny-Cours

processors with a total of 32 cores, 64GB

RAM, and two hierarchy levels.

-

Instance #2 is

jolly

, whose architecture is shown in Fig. 6.

jolly

has four

AMD Opteron 6272

Interlagos

processors with a total of 64 cores, 128GB

RAM, and three hierarchy levels.

Fig. 5.

hwloc

output describing the topology of the

dell32

multicore machine