Hardware Reference

In-Depth Information

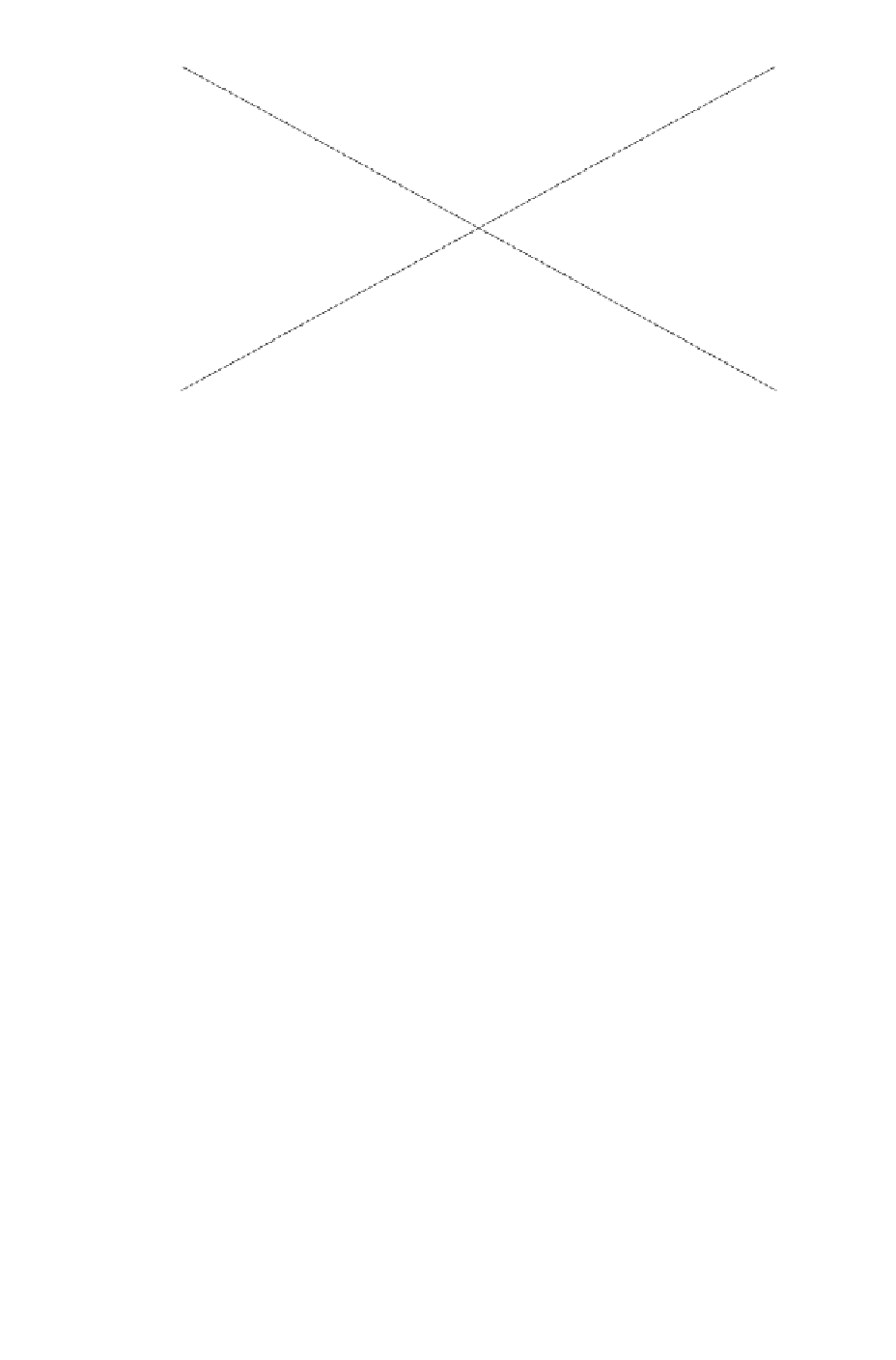

Figure 4.78: Gate signals for the three-phase inverter in the CC-BLDC mode.

In the PWM-BLDC mode, one of the transistors in the “on” state is turned

on and off at the PWM frequency so that either the drive voltage is controlled

by a

fi

xed PWM duty cycle or the current is adjusted by means of an integrated

current control circuit [174]. The PWM signal can be applied only on one

transistor while keeping another transistor “full-on” during the complete step,

or both the high side and the low side transistors are switched off together

during each PWM off period. In this way, the voltage regulator can be saved

which is needed in the CV-BLDC circuit, and in normally the efficiency of the

drive system can be improved. If the PWM BLDC mode works at 100% duty

cycle, it will be the CV-BLDC mode.

The gate signals in the CC-BLDC mode are actually PWM signals with

varying duty cycles, which are different from those with

fi

xed duty cycles in

the PWM BLDC mode. Simulated gate signals for these two modes are shown

in Figure 4.78and Figure 4.79, respectively.

Using CC-BLDC mode or the PWM BLDC introduces signi

fi

cant noises

superimposed on the voltages, as shown in Figure 4.80, which is not desirable

in some applications.

4.4.2.3 Detection of Rotor Position using back-EMF Signal

In using the BLDC mode, only the rotor positions signals at the commutation

points are needed. It is clear that detecting the rotor position accurately at

these points are critical to this drive mode. In the spindle motor, the sensorless

method based on direct back-EMF detection is normally used to detect the

rotor position for realizing the BLDC drive.