Java Reference

In-Depth Information

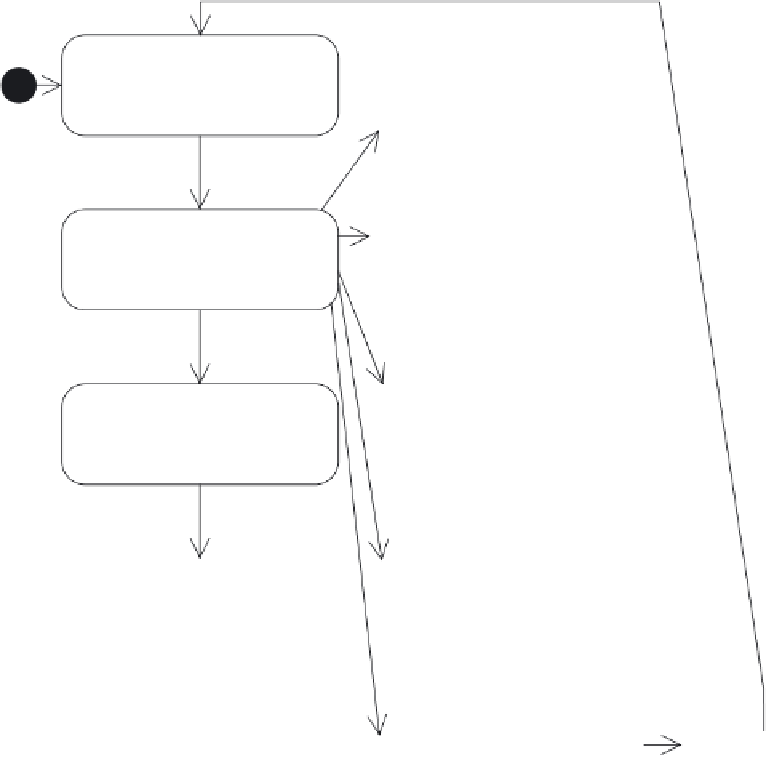

[bus.command

ACK]

FETCH

JUMP

bus.address

PC

bus.command

RAM_READ

PC

arg ( IR )

DECODE

JUMPZ

if ( RegA

0 )

PC

arg( IR )

IR

bus.data

PC

HALT

STOREA

bus.command

RAM_WRITE

bus.data

RegA

bus.address

arg( IR )

MOVEAB

bus.command

RAM_WRITE

bus.data

RegA

bus.address

RegB

[bus.command

ACK]

LOADA

bus.command

RAM_READ

bus.address

arg( IR )

LOADA2

RegA

bus.data

Figure 5.8

FSA for the basic CPU instructions

transition. A few instructions (i.e.

LOADA

,

LOADB

and

MOVEAB

) are more

complex and involve two states.

5.5.3

Implementation

In this prototype we define a package, HDL, which contains all the classes

used for the simulation. The user interface and the test classes are put

outside this package.

The only class that is changed with respect to the previous prototype is

the CPU. In particular we have to implement the execution of instructions as

described in the FSA of Figure 5.8. The instructions are codified as string