Information Technology Reference

In-Depth Information

On) and the bandwidth of IP network 2 can be increased to 80 Mbps, all streams

including the two HDTV' streams and the single 4Kx1K stream can be transmitted

to the projector at site B. In addition, a conventional PC can easily record and play

back the transferred SHR stream at low cost.

5

Two Synchronization Schemes

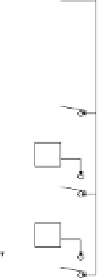

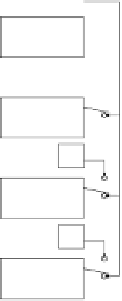

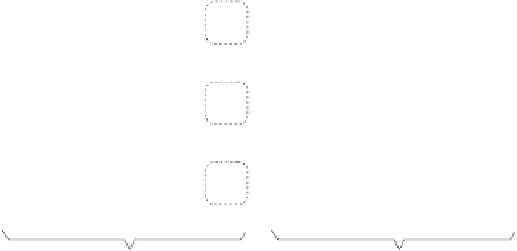

Even if all decoders can input the same PCR packets using the cascade multiplexing

function mentioned above, conventional decoders generate different STCs because

each PLL of conventional decoders is made of different crystal. This indicates the

possibility of sub-images of SHR decoders being displayed without synchroniza-

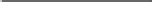

tion. This CODEC system has two schemes to synchronize channels. The first is a

multiplexing mode that shares a common STC, as seen in Fig. 8.

CLK27M

CLK27M

VCO

PLL

STC out

STC out

CLK in

CLK in

STC in

STC in

Video 1

Decoder 1

Video 1

Encoder 1

VCO

PLL

Stream

STC

switch

STC

switch

PLL

switch

PLL

switch

STC out

STC in

STC out

STC in

CLK in

CLK in

Video 2

Decoder 2

Video 2

Encoder 2

VCO

PLL

Stream

STC

switch

STC

switch

PLL

switch

PLL

switch

STC out

STC in

STC out

STC in

CLK in

CLK in

Video 3

Decoder 3

Video 3

Encoder 3

VCO

PLL

Stream

STC

switch

STC

switch

PLL

switch

PLL

switch

STC out

STC in

STC out

STC in

CLK in

CLK in

Video 4

Decoder 4

Video 4

Encoder 4

Stream

SHR main encoder

SHR decoder

Fig. 8

Synchronization achieved by STC sharing in multiplexing mode

To synchronize all input video signals in the encoder system, a 27-MHz sys-

tem clock and an STC value are generated from one of the input video signals

and distributed to the encoders. Each encoder generates a PCR and a Presenting

Time Stamp/Decoding Time Stamp (PTS/DTS) based on the given system clock

and STC value. The decoders consist of one master decoder and several slave de-

coders. The master decoder generates a 27-MHz system clock and an STC from the

received PCRs and distributes the system clock and STC value to the slave decoders.

To deal with deviations in the received timing and to avoid stream buffer under-

flow or overflow, the encoder system generates a PTS/DTS with an adequate timing

margin.