Information Technology Reference

In-Depth Information

Fig. 7.8

Symbol for

reversible carry generation

Table 7.1

Binary addition example

(1 1 1)

111

+111

1110

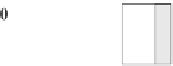

Fig. 7.9

Reversible adder for two 3-bit numbers

input bits are c

in0

, which is the carry into the operation, and the operands a, b.

The carry may be generated as in Fig.

7.8

.

For example, if c

in0

is zero, while a, b are 1, 1, the inputs on the left are

0

,

1

,

1

,

0

.

The carry out is c

1

¼

1. It can be verified by

tracing from left to right that the outputs on the right are

0

,

1

,

1

,

1

as required.

1 since 0 + 1 + 1 equals 0 with c

1

¼

Multiple Bit Numbers

Here is an example of adding two unsigned numbers each with three bits. Shown in

Table

7.1

is an addend of 7 being added to an augend of 7, or in binary 111 + 111.

The carries into the next places are in parenthesis. These numbers correspond to

adding 7 to 7 and arriving at a sum of 14, that is, binary 1110. Figure

7.9

shows how

such addition may be done reversibly.

Operations are executed one at a time, from left to right. First the carries are

generated; sums are then calculated beginning in the most significant place. The

zero inputs to each carry block are “scratchpad” lines for the calculation. As

the sums are computed, the carry programming is reversed to restore the scratchpad

lines back to zero. Interested readers can trace the result of adding 7 + 7. Let

C

in0

¼

0; A0, A1, A2

¼

1, 1, 1; B0, B1, B2

¼

1, 1, 1. The result obtained in this

test case is C

3

, S

2

, S

1

, S

0

¼

1, 1, 1, 0.

Search WWH ::

Custom Search